Chapter 4. Configuration Registers

4-19

Peripheral Logic Power Management Configuration Registers (PMCRs)

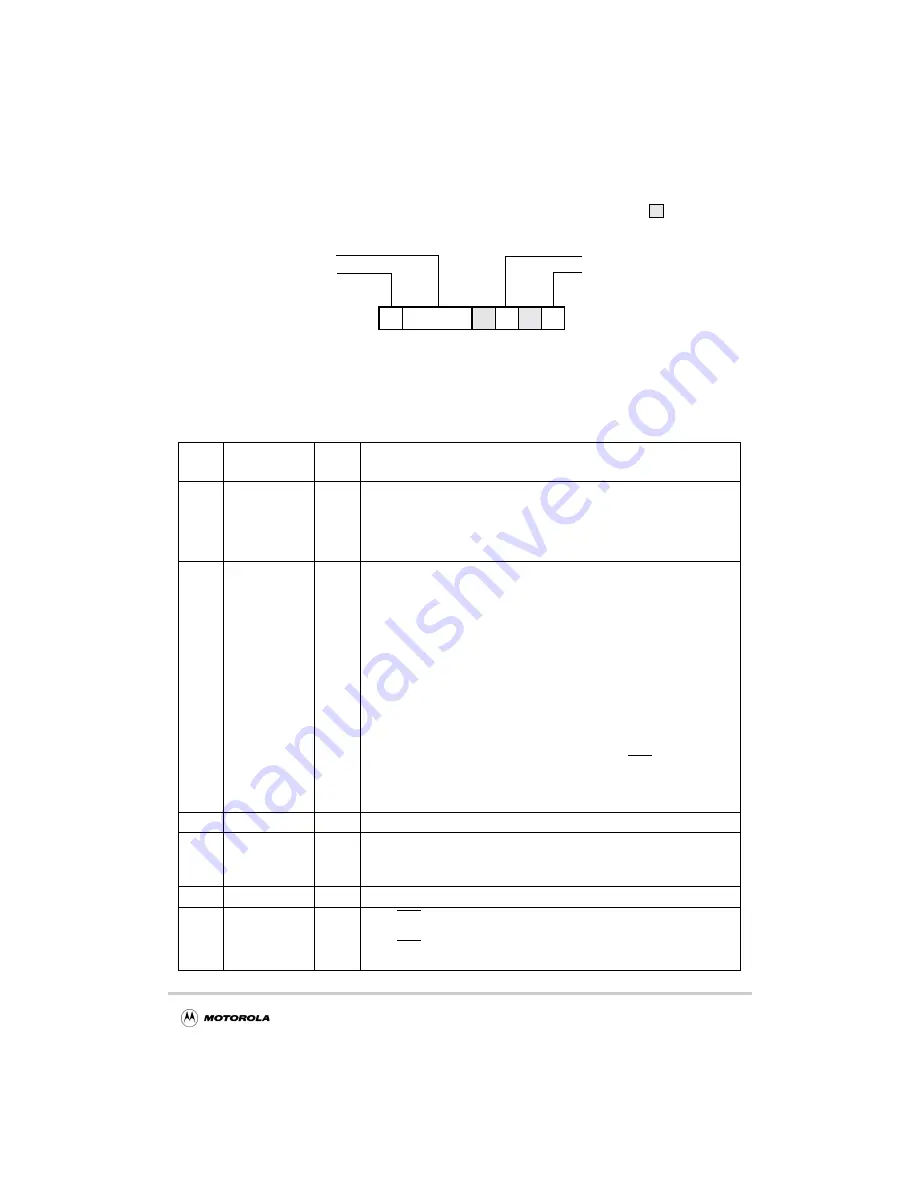

Figure 4-6. Power Management Configuration Register 2 (PMCR2)—0x72

Table 4-16 describes the bits of PMCR2.

Table 4-16. Power Management Configuration Register 2—0x72

Bits

Name

Reset

Value

Description

msb 7

DLL_EXTEND

0

This bit can be used to shift the lock-range of the DLL by half of a PCI clock

cycle. See the MPC8240 Hardware Specification for more information on the

use of the DLL extend feature.

0 DLL extended range

1 Standard (non-extended) range

6–4

PCI_HOLD_DEL

xx0

PCI output hold delay value relative to the PCI_SYNC_IN signal. See the

MPC8240 Hardware Specification for the detailed number of nanoseconds

guaranteed for each setting. There are eight sequential settings for this value;

each corresponds to a set increase in hold time:

000 Recommended for 66 MHz PCI bus

001

010

011

100 Recommended for 33 MHz PCI bus

101

110 Default if reset configuration pins left unconnected

111

The initial values of bits 6 and 5 are determined by the MCP and CKE reset

configuration signals, respectively. See Section 2.4, “Configuration Signals

Sampled at Reset,” for more information. As these two pins have internal

pull-up resistors, the default value after reset is 0b110.

3

—

0

Reserved

2

PLL_SLEEP

0

PLL sampling when waking from sleep mode

0 The MPC8240 does not sample the PLL configuration pins

1 The MPC8240 samples the PLL configuration pins

1

—

0

Reserved

0

SHARED_MCP

0

0 The MCP output is always driven (asserted if there is an error to report;

negated otherwise) by the MPC8420.

1 The MCP output signal is tri-stated when there is no error to report by the

MPC8240.

Reserved

SHARED_MCP

0

0

7

6

4

3

2

1

0

PLL_SLEEP

PCI_HOLD_DELAY[0–2]

DLL_EXTEND

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...