Chapter 4. Configuration Registers

4-33

Error Handling Registers

4.8 Error Handling Registers

Chapter 13, “Error Handling,” describes specific error conditions and how the MPC8240

responds to them. The registers at offsets 0xB8, 0xB9, and 0xC0 through 0xCB control the

error handling and reporting for the MPC8240. The following sections provide descriptions

of these registers.

4.8.1 ECC Single-Bit Error Registers

The ECC single-bit error registers are two 8-bit registers used to control the reporting of

ECC single-bit errors. See Chapter 13, “Error Handling,” for more information. The ECC

single-bit error counter, shown in Figure 4-19, maintains a count of the number of single-bit

errors that have been detected. It is a read/write register that is cleared to 0x00 whenever

any data is written to it.

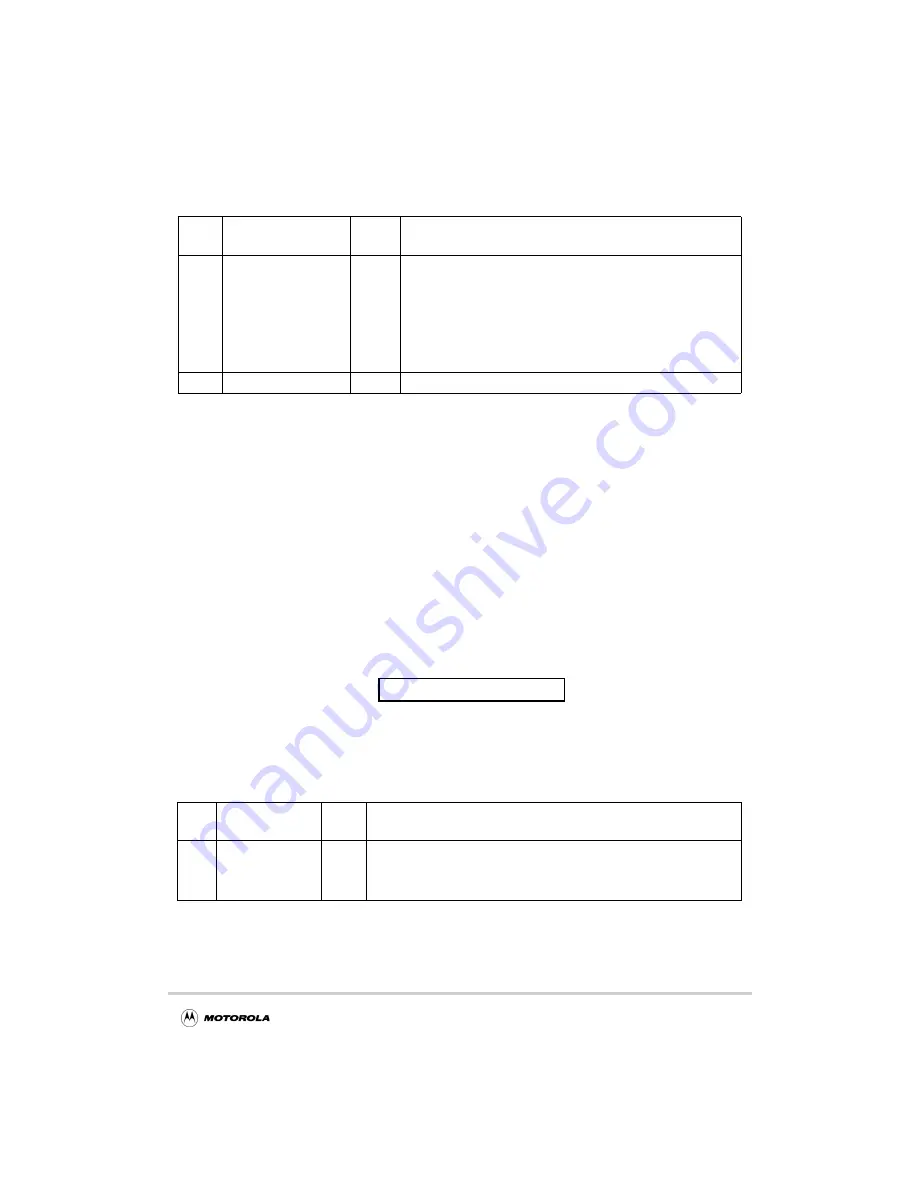

Figure 4-19. ECC Single-Bit Error Counter Register—0xB8

Table 4-28 describes the bits of the ECC single-bit error counter.

The ECC single-bit error trigger, shown in Figure 4-20, provides a threshold value that,

when equal to the single-bit error count, triggers the MPC8240 error reporting logic.

3–2

CF_IP2

11

Internal parameter 2

00 Use for optimal performance.

01 Reserved; do not use.

10 Reserved; do not use.

11 Default; however should be changed to 0b00 for optimal

performance.

1–0

—

00

Reserved

Table 4-28. Bit Settings for ECC Single-Bit Error Counter Register—0xB8

Bits

Name

Reset

Value

Description

7–0

ECC single-bit error

counter

All 0s

These bits maintain a count of the number of ECC single-bit errors that have

been detected and corrected. If this value equals the value contained in the

ECC single-bit error trigger register, then an error is reported (provided

ErrEnR1[2] = 1).

Table 4-27. Bit Settings for PICR2—0xAC (Continued)

Bits

Name

Reset

Value

Description

ECC Single-Bit Error Counter

7

0

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...