Chapter 4. Configuration Registers

4-35

Error Handling Registers

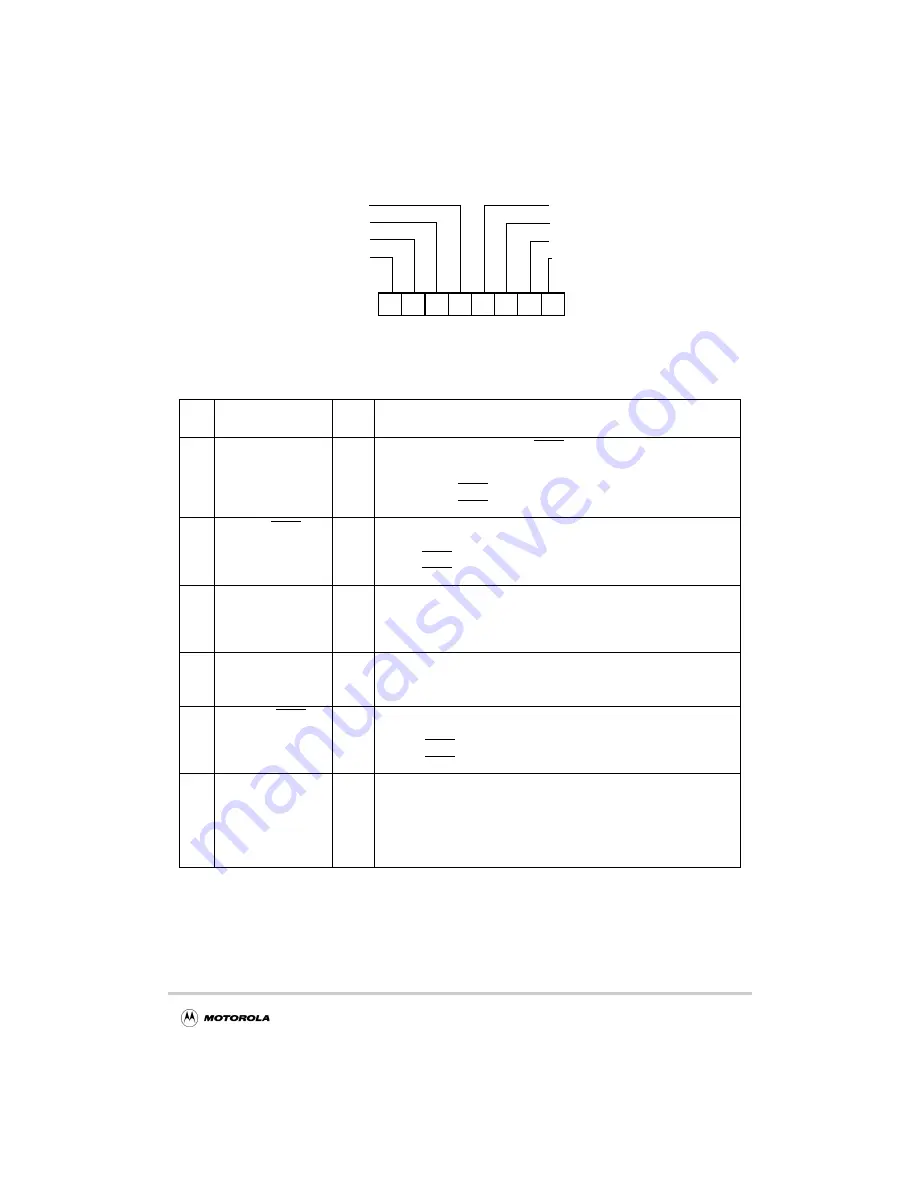

Figure 4-21. Error Enabling Register 1 (ErrEnR1)—0xC0

Table 4-30. Bit Settings for Error Enabling Register 1 (ErrEnR1)—0xC0

Bits

Name

Reset

Value

Description

7

RX_SERR_EN

0

This bit enables the reporting of SERR assertions that occur on the PCI

bus two clock cycles after the address phase of transactions where the

MPC8240 is the initiator.

0 Received PCI SERR disabled

1 Received PCI SERR enabled

6

PCI target PERR

enable

0

This bit enables the reporting of data parity errors on the PCI bus for

transactions involving the MPC8240 as a target.

0 Target PERR disabled

1 Target PERR enabled

5

Memory select error

enable

0

This bit enables the reporting of memory select errors that occur on

(attempted) accesses to system memory.

0 Memory select error disabled

1 Memory select error enabled

4

Memory refresh

overflow enable

0

This bit enables the reporting of memory refresh overflow errors.

0 Memory refresh overflow disabled

1 Memory refresh overflow enabled

3

PCI master PERR

enable

0

This bit enables the reporting of data parity errors on the PCI bus for

transactions involving the MPC8240 as a master.

0 Master PERR disabled

1 Master PERR enabled

2

Memory parity/ECC

enable

0

This bit enables the reporting of system memory read parity errors that

occur on accesses to system memory or those that exceed the ECC

single-bit error threshold. [For SDRAM with in-line ECC/parity, this is the

memory write parity enable bit.]

0 Memory read parity/ECC single-bit threshold disabled

1 Memory read parity/ECC single-bit threshold enabled

7

6

5

4

3

2

1

0

RX_SERR_EN

Memory Select Error Enable

PCI Target PERR Enable

Memory Parity/ECC Enable

Processor Transaction Error Enable

PCI Master-Abort Error Enable

Memory Refresh Overflow Enable

PCI Master PERR Enable

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...