Chapter 5. PowerPC Processor Core

5-13

Programming Model

5.3.1.2 MPC8240-Specific Registers

The set of registers specific to the MPC603e are shown in Figure 5-2. Most of these are

described in the MPC603e User’s Manual and are implemented in the MPC8240 as

follows:

•

MMU software table search registers—DMISS, DCMP, HASH1, HASH2, IMISS,

ICMP, and RPA. These registers facilitate the software required to search the page

tables in memory.

•

IABR—This register facilitates the setting of instruction breakpoints.

The hardware implementation-dependent registers (HIDx) are implemented differently in

the MPC8240 as described in the following subsections.

5.3.1.2.1 Hardware Implementation-Dependent Register 0 (HID0)

The processor core’s implementation of HID0 differs from the MPC603e User’s Manual as

follows:

•

Bit 5, HID0[EICE], has been removed

•

No support for pipeline tracking

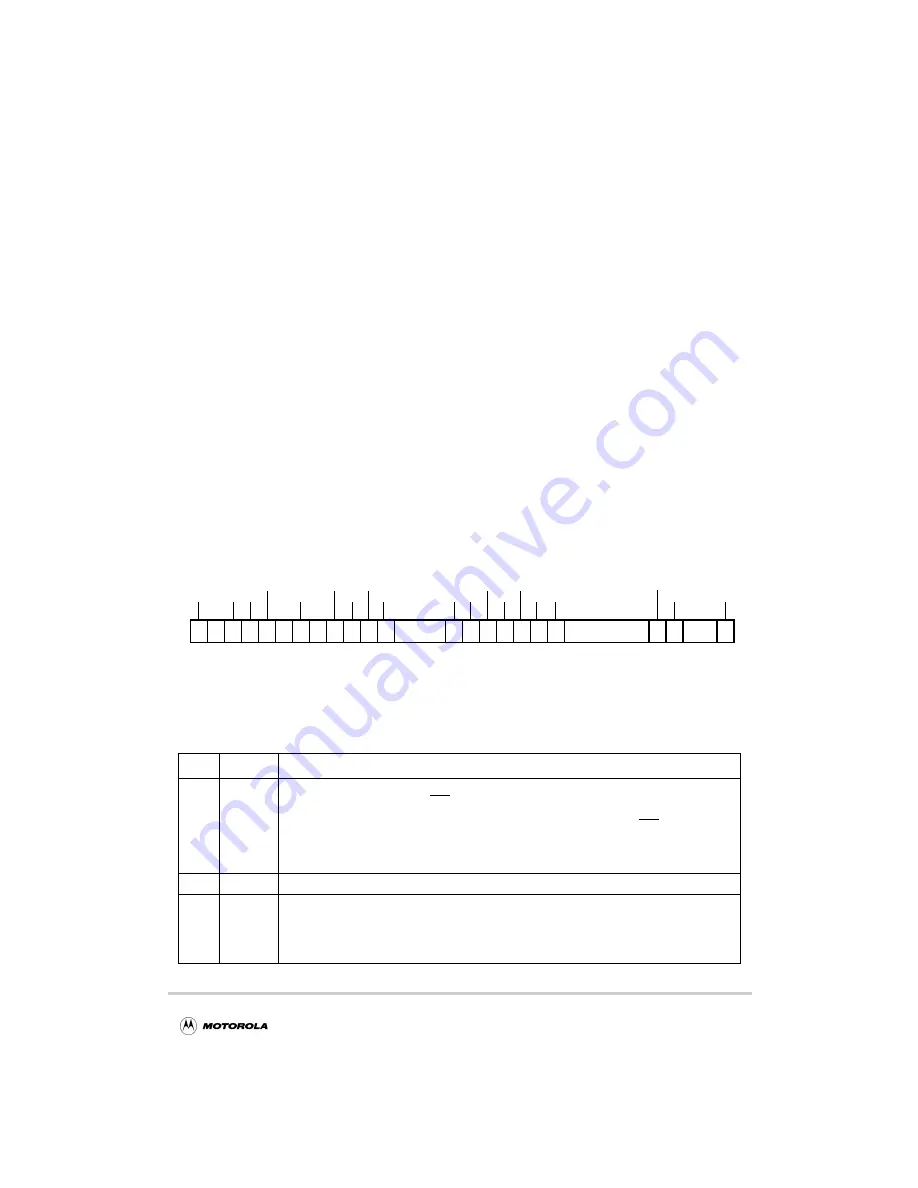

Figure 5-3 shows the MPC8240 implementation of HID0. HID0 can be accessed with

mtspr and mfspr using SPR1008.

Figure 5-3. Hardware Implementation Register 0 (HID0)

Table 5-1 shows the bit definitions for HID0.

Table 5-1. HID0 Field Descriptions

Bits

Name

Description

0

EMCP

Enable machine check internal signal

0 The assertion of the internal mcp signal from the peripheral logic does not cause a machine

check exception.

1 Enables the machine check exception based on assertion of the internal mcp signal from the

peripheral logic to the processor core.

Note that the machine check exception is further affected by MSR[ME], which specifies whether

the processor checkstops or continues processing.

1

—

Reserved

2

EBA

Enable/disable internal peripheral bus (60x bus) address parity checking

0 Prevents address parity checking

1 Allows a address parity error to cause a checkstop if MSR[ME] = 0 or a machine check

exception if MSR[ME] = 1

EBA and EBD let the processor operate with memory subsystems that do not generate parity.

—

—

—

—

—

—

0

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

EMCP

EBA EBD

ECLK

NAP

DPM

NHR ICE

ILOCK

DLOCK

ICFI DCFI

ABE

NOOPTI

DCE

SLEEP

DOZE

SBCLK

FBIOB

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...