5-24

MPC8240 Integrated Processor User’s Manual

Cache Implementation

Unlike entire cache locking, invalid entries in a locked way are accessible and available for

data placement. As hits to the cache fill invalid entries within a locked way, the entries

become valid and locked. This behavior differs from entire cache locking where nothing is

placed in the cache, even if invalid entries exist in the cache. Unlocked ways of the cache

behave normally.

5.4.3 Cache Coherency

The central control unit (CCU) manages the cache coherency within the MPC8240. It

responds to all accesses generated by the processor core and causes the snooping of the

addresses in the internal buffers as necessary. Also, the CCU generates snoop transactions

on the peripheral logic bus to allow the processor to snoop accesses between the PCI

interface and memory. Refer to Chapter 7, “PCI Bus Interface,” for more detailed

information about the internal address and data buffers in the MPC8240.

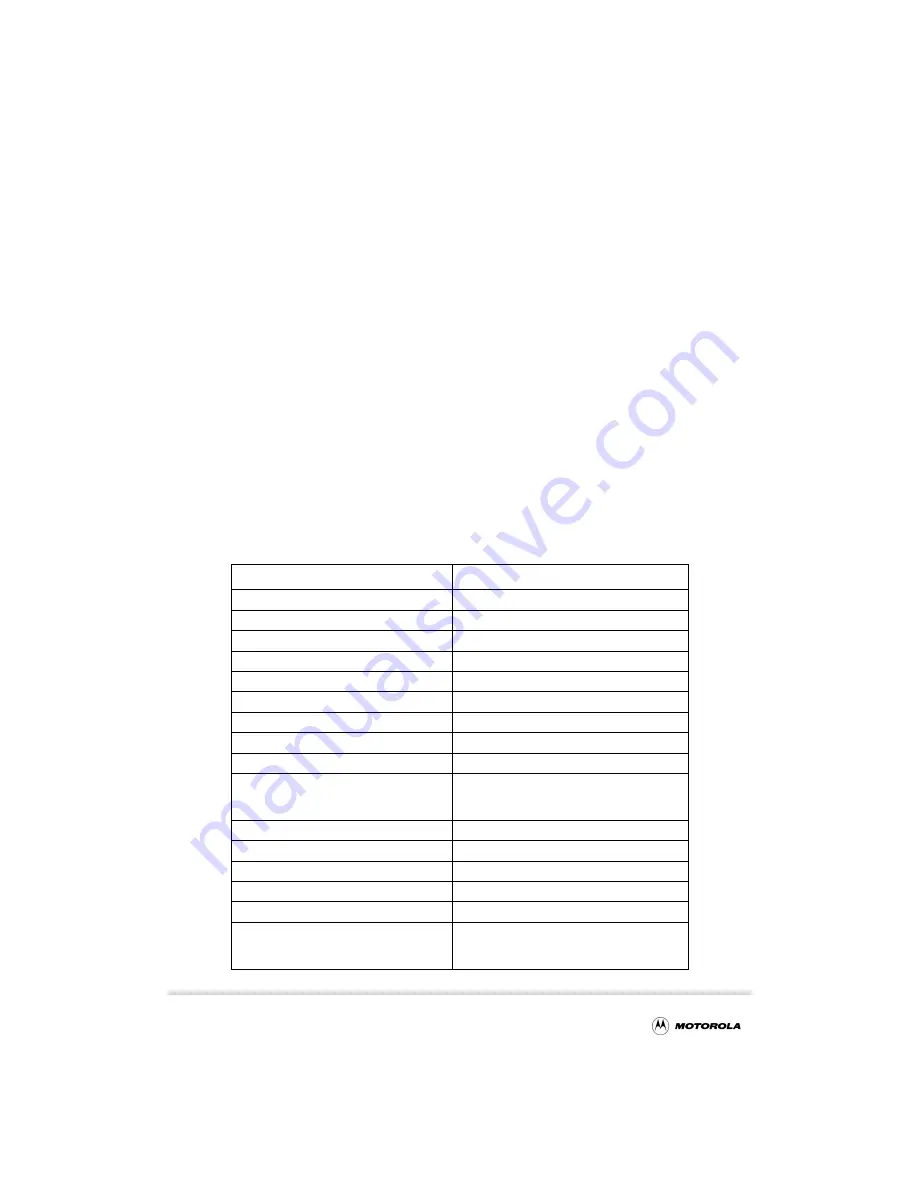

5.4.3.1 CCU Responses to Processor Transactions

The processor core generates various types of read and write accesses as well as

address-only transactions. Table 5-5 shows all the types of internal transactions performed

by the processor core and the CCU responses.

Table 5-5. CCU Responses to Processor Transactions

Processor Transaction

CCU Response

Read

Directs read to appropriate interface

Read-with-intent-to-modify

Directs read to appropriate interface

Read atomic

Directs read to appropriate interface

Read-with-intent-to-modify-atomic

Directs read to appropriate interface

Write-with-flush

Directs write to appropriate interface

Write-with-kill

Directs write to appropriate interface

Write-with-flush-atomic

Directs write to appropriate interface

sync

CCU buffers are flushed.

eieio

CCU buffers are flushed.

Kill block (generated by dcbz instruction

when the addressed block has either the E

or M bits set)

CCU buffers are snooped.

icbi

CCU buffers are snooped.

Read-with-no-intent-to-cache

Directs read to appropriate interface

Clean

CCU takes no further action.

Flush

CCU takes no further action.

tlbie

CCU takes no further action.

lwarx, reservation set

CCU takes no further action.

(The MPC8240 does not support atomic

references in PCI memory space.)

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...