Chapter 6. MPC8240 Memory Interface

6-25

SDRAM Interface Operation

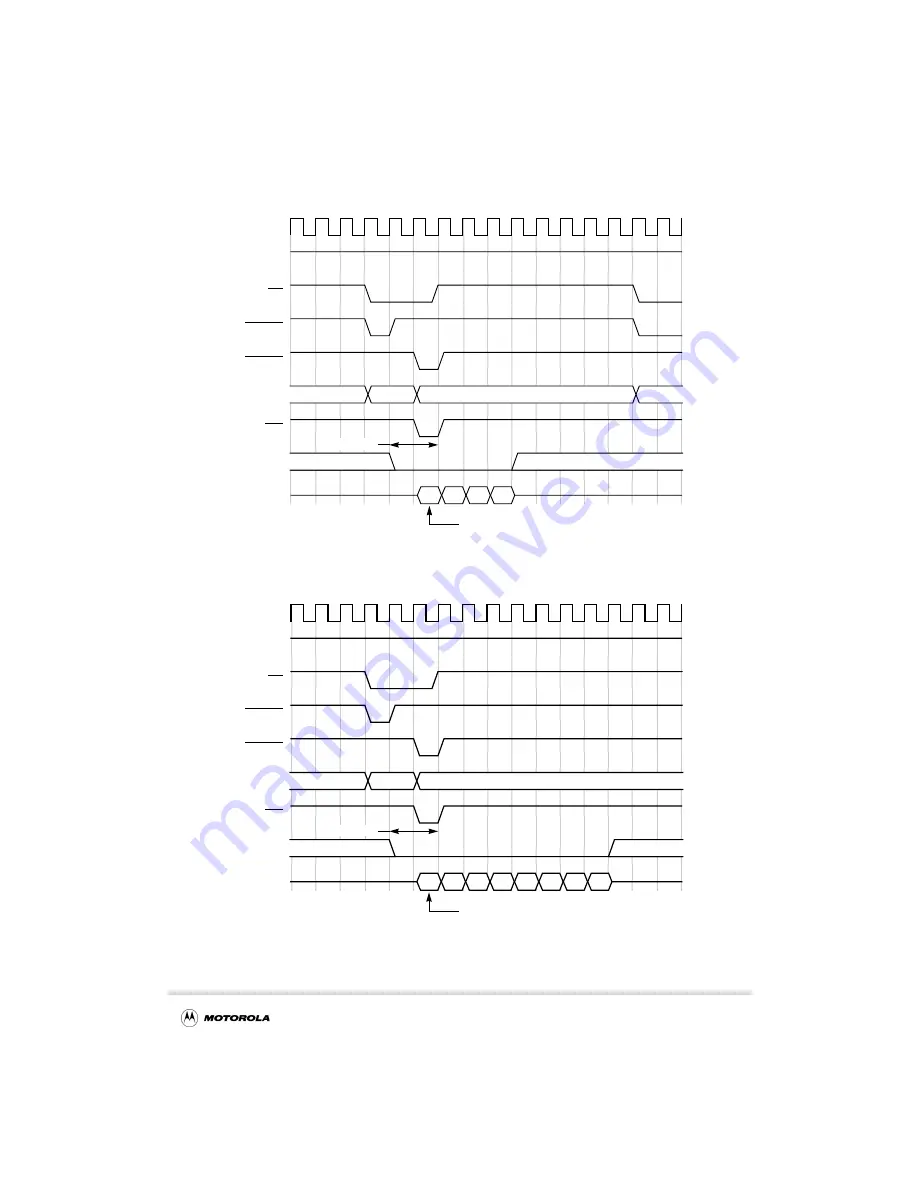

Figure 6-12 shows a four-beat burst-write operation.

Figure 6-12. SDRAM Four-Beat Burst Write Timing—64-Bit Mode

Figure 6-13. SDRAM Eight-Beat Burst Write Timing—32-Bit Mode

SDRAM

CKE

CS

SDRAS

SDCAS

WE

COL

ADDR

DQM[0:7]

DATA

ROW

ROW

ACTORW

Write

CLK[0:3]

DQM and data latency = 0 for writes

D0

D1

D2

D3

SDRAM

CKE

CS

SDRAS

SDCAS

WE

COL

ADDR

DQM[0:7]

DATA

ROW

ACTORW

Write

CLK[0:3]

DQM and data latency = 0 for writes

D0

D1

D2

D3

D4

D5

D6

D7

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...