6-28

MPC8240 Integrated Processor User’s Manual

SDRAM Interface Operation

The in-line ECC and parity data path option allows the MPC8240 to detect and

automatically correct single bit ECC errors; detect multiple bit ECC errors or parity errors

with only one clock cycle penalty on CPU and PCI memory read operations; and generate

parity for the internal processor data bus. For CPU and PCI memory write operations, parity

can be checked automatically on the internal processor data bus and either ECC or parity

generated for the memory bus. Table 6-8 and Table 6-9 describe the configuration

requirements for this mode.

The in-line ECC logic in the MPC8240 detects and corrects all single-bit errors and detects

all double-bit errors and all errors within a nibble. Other errors are not guaranteed to be

detected or corrected. Multiple-bit errors are always reported if detected. However, when a

single-bit error occurs, the value in the ECC single bit error counter register is compared to

the ECC single bit error trigger register. If the values are not equal, no error is reported; if

the values are equal, then an error is reported. Thus, the single-bit error registers may be

programmed so that minor faults with memory are corrected and ignored, but a catastrophic

memory failure generates an interrupt. See Section 4.8.1, “ECC Single-Bit Error

Registers,” for more information on these registers.

The MPC8240 supports concurrent ECC for the memory data path and parity for the local

processor data path. ECC and parity may be independently enabled or disabled. The eight

signals used for ECC (PAR[0:7]) are also used for processor core parity. The MPC8240

checks ECC on 64-bit memory reads.

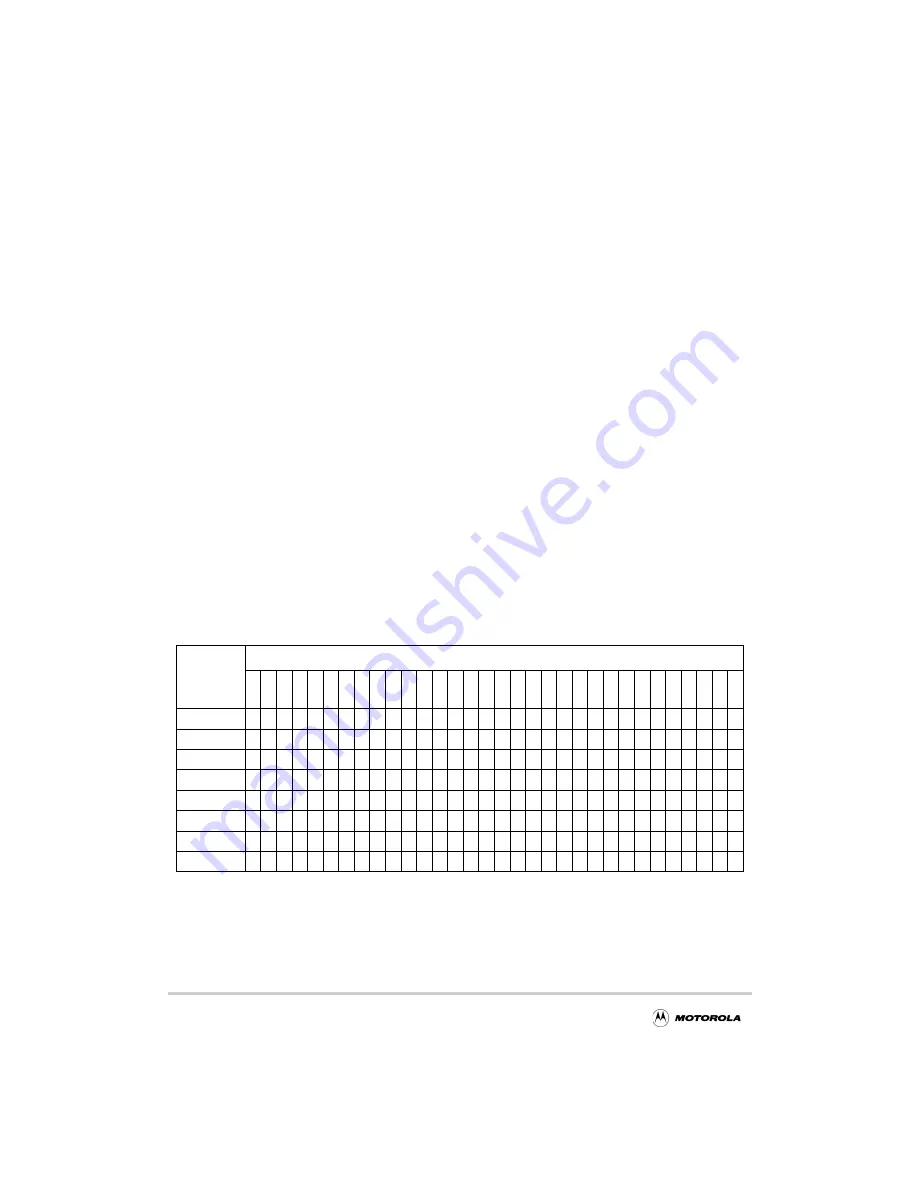

The syndrome equations for the ECC codes are shown in Table 6-12 and Table 6-13.

Table 6-12. The MPC8240 SDRAM ECC Syndrome Encoding (Data Bits 0:31)

Syndrome

Bit

Data Bit

0 1 2 3 4 5 6 7 8 9

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

3

1

0

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

1

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

2

x

x

x

x

x

x

x

x

3

x

x

x

x

x

x

x

x

4

x

x

x

x

x

x

x

x

x

x

x

x

5

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

6

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

7

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...