7-10

MPC8240 Integrated Processor User’s Manual

PCI Bus Protocol

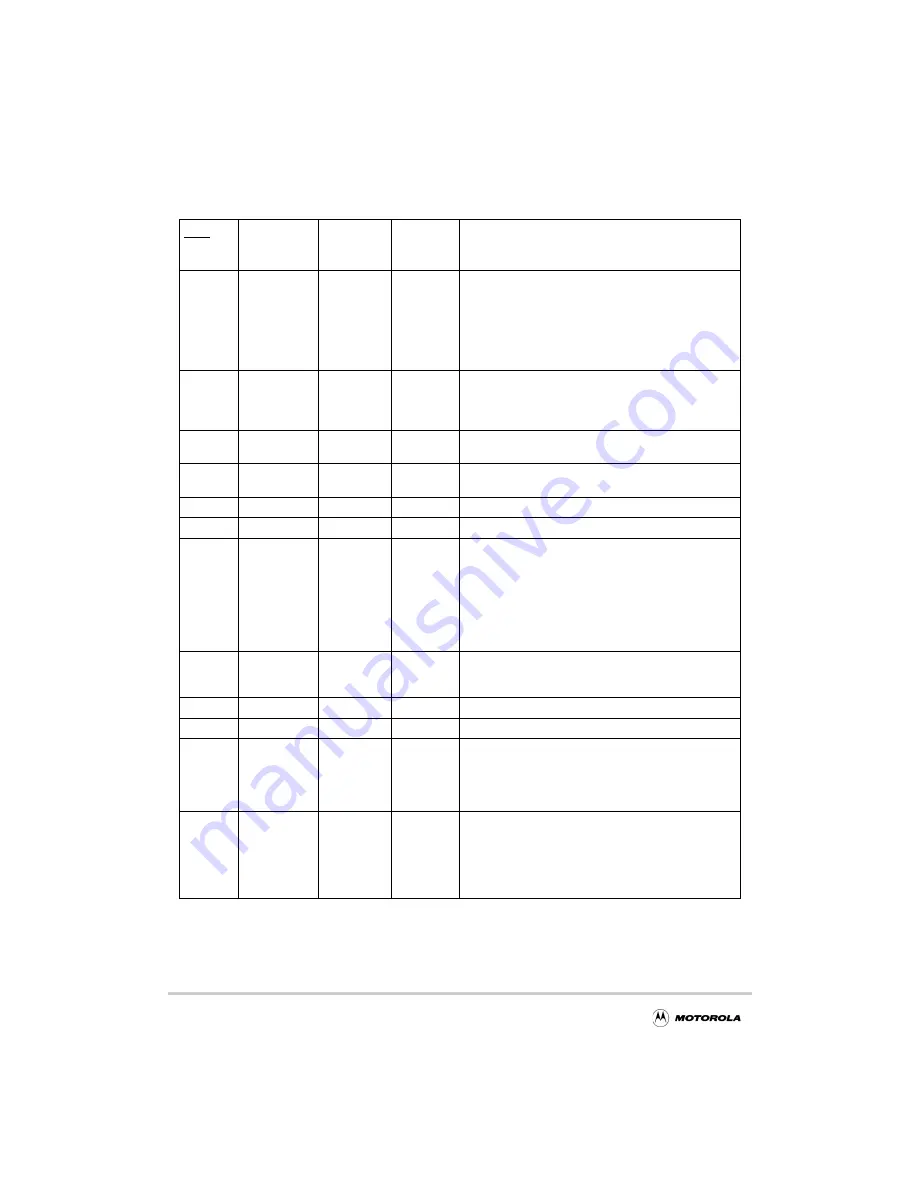

Table 7-2. PCI Bus Commands

C/BE[3:0]

PCI Bus

Command

MPC8240

Supports as

an Initiator

MPC8240

Supports

as a Target

Definition

0000

Interrupt-

acknowledge

Yes

No

The interrupt-acknowledge command is a read (implicitly

addressing the system interrupt controller). Only one

device on the PCI bus should respond to the

interrupt-acknowledge command. Other devices ignore

the interrupt-acknowledge command. See

Section 7.4.6.1, “Interrupt-Acknowledge Transactions,”

for more information.

0001

Special cycle

Yes

No

The special-cycle command provides a mechanism to

broadcast select messages to all devices on the PCI bus.

See Section 7.4.6.2, “Special-Cycle Transactions,” for

more information.

0010

I/O-read

Yes

No

The I/O-read command accesses agents mapped into

the PCI I/O space.

0011

I/O-write

Yes

No

The I/O-write command accesses agents mapped into

the PCI I/O space.

0100

Reserved

1

No

No

—

0101

Reserved

1

No

No

—

0110

Memory-read

Yes

Yes

The memory-read command accesses either local

memory or agents mapped into PCI memory space,

depending on the address. When a PCI master issues a

memory-read command to local memory, the MPC8240

(the target) fetches data from the requested address to

the end of the cache line (32 bytes) from local memory,

even though all of the data may not be requested by (or

sent to) the initiator.

0111

Memory-write

Yes

Yes

The memory-write command accesses either local

memory or agents mapped into PCI memory space,

depending on the address.

1000

Reserved

1

No

No

—

1001

Reserved

1

No

No

—

1010

Configuration-

read

Yes

Yes

The configuration-read command accesses the 256-byte

configuration space of a PCI agent. A specific agent is

selected when its IDSEL signal is asserted during the

address phase. See Section 7.4.5, “Configuration

Cycles,” for more detail on PCI configuration cycles.

1011

Configuration-

write

Yes

Yes

The configuration-write command accesses the 256-byte

configuration space of a PCI agent. A specific agent is

selected when its IDSEL signal is asserted during the

address phase. See Section 7.4.5.2, “Accessing the PCI

Configuration Space,” for more detail on PCI

configuration accesses.

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...