9-4

MPC8240 Integrated Processor User’s Manual

Message and Doorbell Register Programming Model

Table 9-4 shows the bit settings for the IDBR.

Alternatively, theMPC8240 processor core can write to the ODBR, which causes the

outbound interrupt signal INTA to be asserted, thus interrupting a remote processor if the

interrupt is not masked in OMIMR. When INTA is generated, it can only be cleared by the

remote processor (through PCI) by writing a 1 to the bits that are set in the ODBR. The

processor core can only generate INTA through the ODBR, and it can not clear this

interrupt.

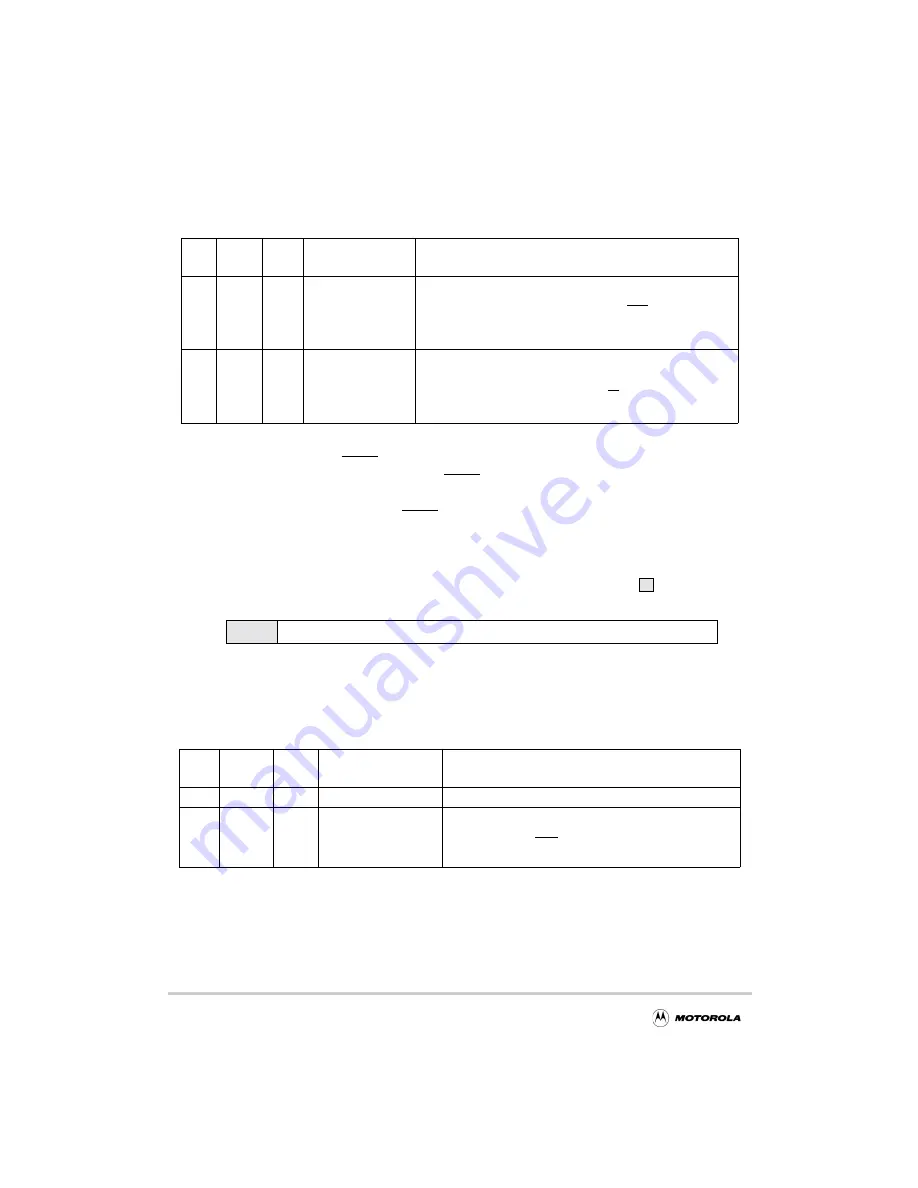

Figure 9-3 shows the ODBR.

Figure 9-3. Outbound Doorbell Register (ODBR)

Table 9-5 shows the bit settings for the ODBR.

Table 9-4. IDBR Field Descriptions—Offsets 0x068, 0x0_0068

Bits

Name

Reset

Value

R/W

Description

31

MC

0

R/W. A write of 1

from PCI sets the bit;

a write of 1 from the

processor core

clears the bit.

Machine check

0 No machine check

1 Writing to this bit causes the assertion of mcp to the processor

core if IMIMR[DMCM] = 0; it also causes IMISR[DMC] to be set.

30–0

DBn

All 0s

R/W. A write of 1

from PCI sets the bit;

a write of 1 from the

processor core

clears the bit.

Inbound doorbell n interrupt, where n is each bit

0 No inbound doorbell interrupt

1 Setting any bit in this register from the PCI bus causes an

interrupt to be generated through the int signal to the processor

core if IMIMR[IDIM] = 0; it also causes IMISR[IDI] to be set.

Table 9-5. ODBR Field Descriptions—Offsets 0x060, 0x0_0060

Bits

Name

Reset

Value

R/W

Description

31–29

—

000

R

Reserved

28–0

DBn

All 0s

R/W. A write of 1 from

the processor core sets

the bit; a write of 1 from

PCI clears the bit.

Outbound doorbell interrupt n where n is each bit. Writing

any bit in this register from the processor core causes an

external interrupt (INTA) to be signalled if IMIMR[ODIM] = 0;

it also causes OMISR[ODI] to be set

0 0 0

DBn

31

29 28

0

Reserved

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...