9-16

MPC8240 Integrated Processor User’s Manual

I

2

O Interface

Table 9-15 shows the bit settings for the IFHPR.

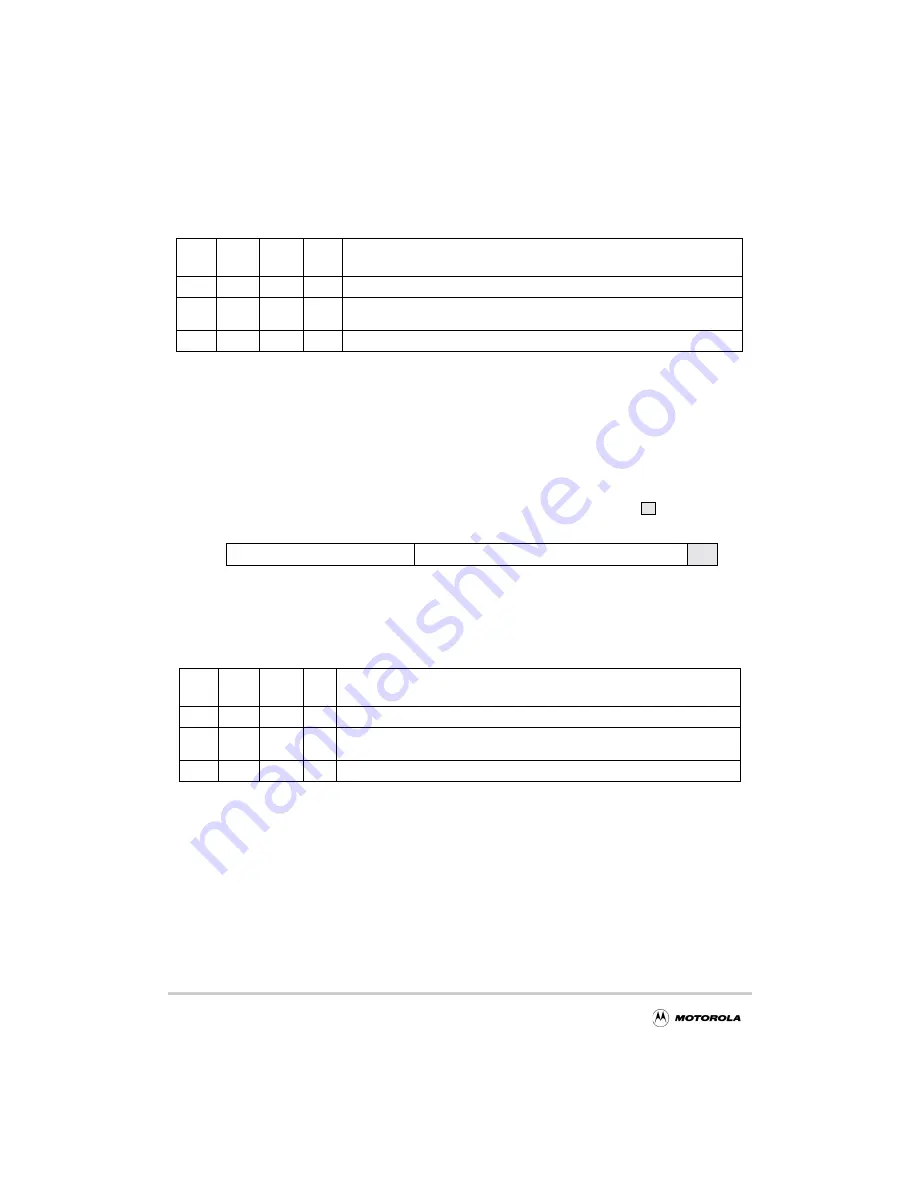

9.3.4.2.4 Inbound Free_FIFO Tail Pointer Register (IFTPR)

PCI masters pick up free MFAs from the inbound free_list FIFO pointed to by the inbound

free_FIFO tail pointer register (IFTPR). The actual PCI reads of MFAs are performed

through the inbound FIFO queue port register (IFQPR). The MPC8240 automatically

increments the IFTP value after every read from IFQPR. Figure 9-12 shows the bits of the

IFTPR.

Figure 9-12. Inbound Free_FIFO Tail Pointer Register (IFTPR)

Table 9-16 shows the bit settings for the IFTPR.

9.3.4.2.5 Inbound Post_FIFO Head Pointer Register (IPHPR)

PCI masters post MFAs to the inbound post_list FIFO pointed to by the inbound post_FIFO

head pointer register (IPHPR). The actual PCI writes are performed through the inbound

FIFO queue port register (IFQPR). The MPC8240 automatically increments the IPHP value

after every write to IFQPR. Figure 9-13 shows the bits of the IPHPR.

Table 9-15. IFHPR Field Descriptions—Offset 0x0_0120

Bits

Name

Reset

Value

R/W

Description

31–20

QBA

All 0s

R

Queue base address. When read, this field returns the contents of QBAR[31–20].

19–2

IFHP

All 0s

RW

Inbound free_FIFO head pointer. The processor maintains the local memory offset

of the head pointer of the inbound free _list FIFO in this field.

1–0

—

00

R

Reserved

Table 9-16. IFTPR Field Descriptions—Offset 0x0_0128

Bits

Name

Reset

Value

R/W

Description

31–20

QBA

All 0s

R

Queue base address. When read, this field returns the contents of QBAR[31–20].

19–2

IFTP

All 0s

RW

Inbound free_FIFO tail pointer. Maintains the local memory offset of the tail pointer

of the inbound free _list FIFO.

1–0

—

00

R

Reserved

QBA

IFTP

0 0

31

20 19

2

1

0

Reserved

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...