Chapter 10. I

2

C Interface

10-13

Programming Guidelines

10.3.5 I

2

C Data Register (I2CDR)

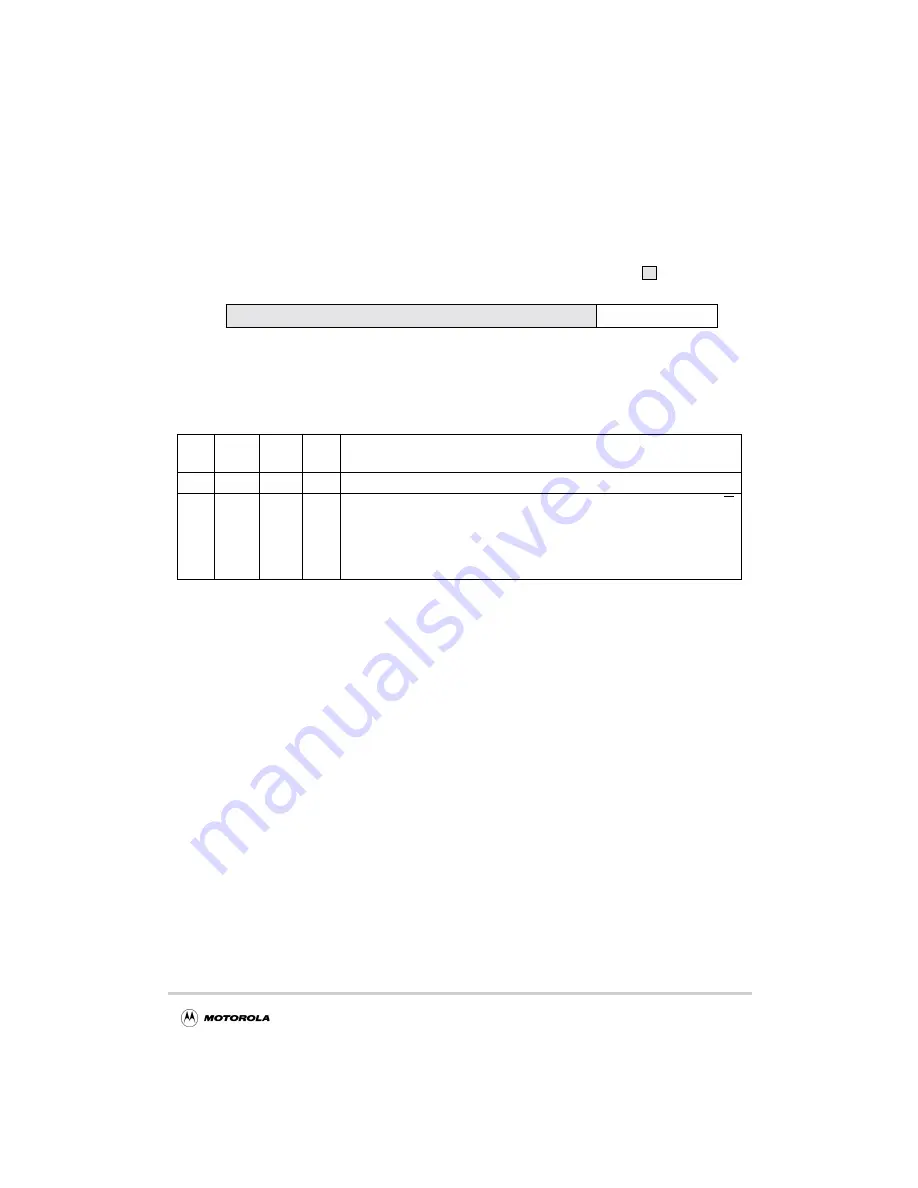

The data register is shown in Figure 10-7.

Figure 10-7. I

2

C Data Register (I2CDR)

10.4 Programming Guidelines

This section describes some programming guidelines recommended for the I

2

C interface

on the MPC8240. Also included is a recommended flowchart for the I

2

C interrupt service

routines.

The I

2

C registers in this chapter are shown in little-endian format. If the system is in

big-endian mode, software must swap the bytes appropriately. Also, a sync assembly

instruction should be executed after each I

2

C register read/write access to guarantee

in-order execution.

The MPC8240 does not guarantee it will recover from all illegal I

2

C bus activity. In

addition, a malfunctioning device may hold the bus captive. A good programming practice

is for software to rely on a watchdog timer to help recover from I

2

C bus hangs. The recovery

routine should also handle the case when the status bits returned after an interrupt are not

consistent with what was expected due to illegal I

2

C bus protocol behavior.

Example I

2

C code can be found in the MPC8240 Device Driver Toolbox available through

the PowerPC web site: www.mot.com/SPS/PowerPC/teksupport/faqsolutions/code (using

the ‘code samples’ link for the Dink drivers directory).

Table 10-8. I2CDR Field Descriptions—Offset 0x0_3010

Bits

Name

Reset

Value

R/W

Description

31–8

—

R

Reserved

7–0

DATA

0x00

R/W

Transmission starts when a 7-bit address is written to bits 7–1 of this field, the R/W

bit (I2CCR[MTX]) is set, and the I

2

C interface is the master. A data transfer is

initiated when data is written to the I2CDR. The most significant bit (msb) is sent

first in both cases. In the master receive mode, reading the data register allows the

read to occur but also initiates next byte data receiving. In slave mode, the same

function is available after it is addressed.

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Data

31

8

7

0

Reserved

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...