Chapter 11. Embedded Programmable Interrupt Controller (EPIC) Unit

11-7

EPIC Unit Interrupt Protocol

11.3 EPIC Unit Interrupt Protocol

The following sections describe the priority of interrupts controlled by the EPIC unit, the

interrupt acknowledge mechanism, the nesting of multiple interrupts, and the handling of

spurious interrupts.

11.3.1 Interrupt Source Priority

The software assigns a priority value to each interrupt source by writing to the

vector/priority register for the particular source. Priority values are in the range 0 to 15 of

which 15 is the highest. In order for an interrupt to be signalled to the processor, the priority

of the source must be greater than that of the current task priority of the processor (and the

in-service interrupt source priority). Therefore, setting a source priority to zero inhibits that

interrupt.

The EPIC unit services simultaneous interrupts occurring with the same priority according

to the following set order: timer 0–timer 3, DMA 0, DMA 1, MU, I

2

C, direct interrupts

from IRQ[0:4] (or serial interrupt source).

11.3.2 Processor Current Task Priority

The EPIC unit has a processor current task priority register (PCTPR) set by system software

to indicate the relative importance of the task running on the processor. When an interrupt

has a priority level greater than the current task priority (and the in-service interrupt source

priority), it is signalled to the processor. Therefore, setting the task priority to 15 in the

PCTPR prevents the signalling of any interrupt to the processor.

0x5_10D0

Message unit interrupt destination register (IIDR3)

P0

0x5_10E0–0x5_FFF0

Reserved

—

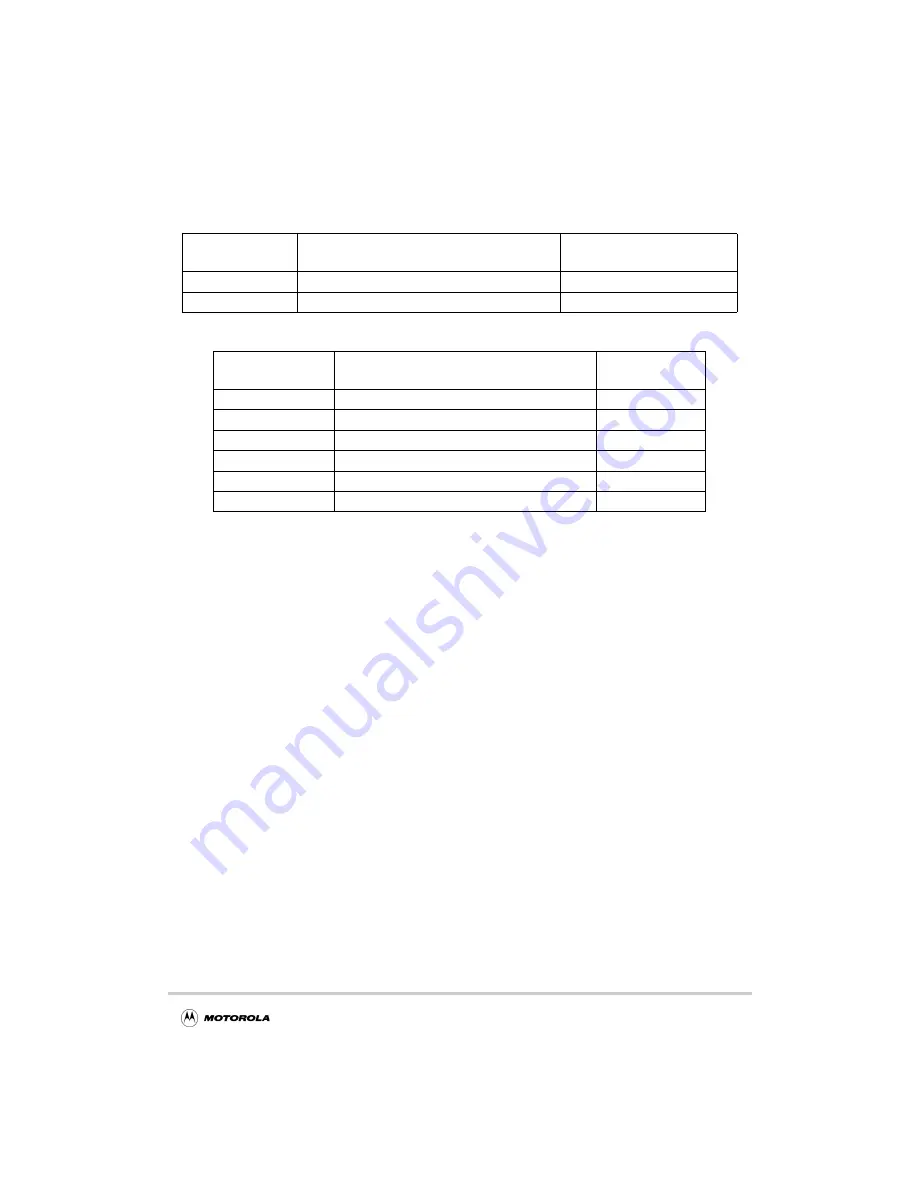

Table 11-4. EPIC Register Address Map—Processor-Related Registers

Address Offset

from EUMBBAR

Register Name

Field Mnemonics

0x6_0000–0x6_0070

Reserved

—

0x6_0080

Processor current task priority register (PCTPR)

TASKP

0x6_0090

Reserved

—

0x6_00A0

Processor interrupt acknowledge register (IACK)

VECTOR

0x6_00B0

Processor end-of-interrupt register (EOI)

EOI_CODE

0x6_00C0–0x6_3FF0

Reserved

—

Table 11-3. EPIC Register Address Map—Interrupt Source

Configuration Registers (Continued)

Address Offset

from EUMBBAR

Register Name

Field Mnemonics

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...