11-20

MPC8240 Integrated Processor User’s Manual

Register Definitions

Table 11-10 describes the bit settings for the SVR.

11.9.7 Global Timer Registers

This section describes the global timer registers. Note that each of the four timers (timer

0–timer 3) has four individual configuration registers (GTCCRn, GTBCRn, GTVPRn,

GTDRn), but they are shown only once in this section.

11.9.7.1 Timer Frequency Reporting Register (TFRR)

The TFRR is written by software to report the clocking frequency of the EPIC timers. Note

that although this register is read/write, the value in this register is ignored by the EPIC unit.

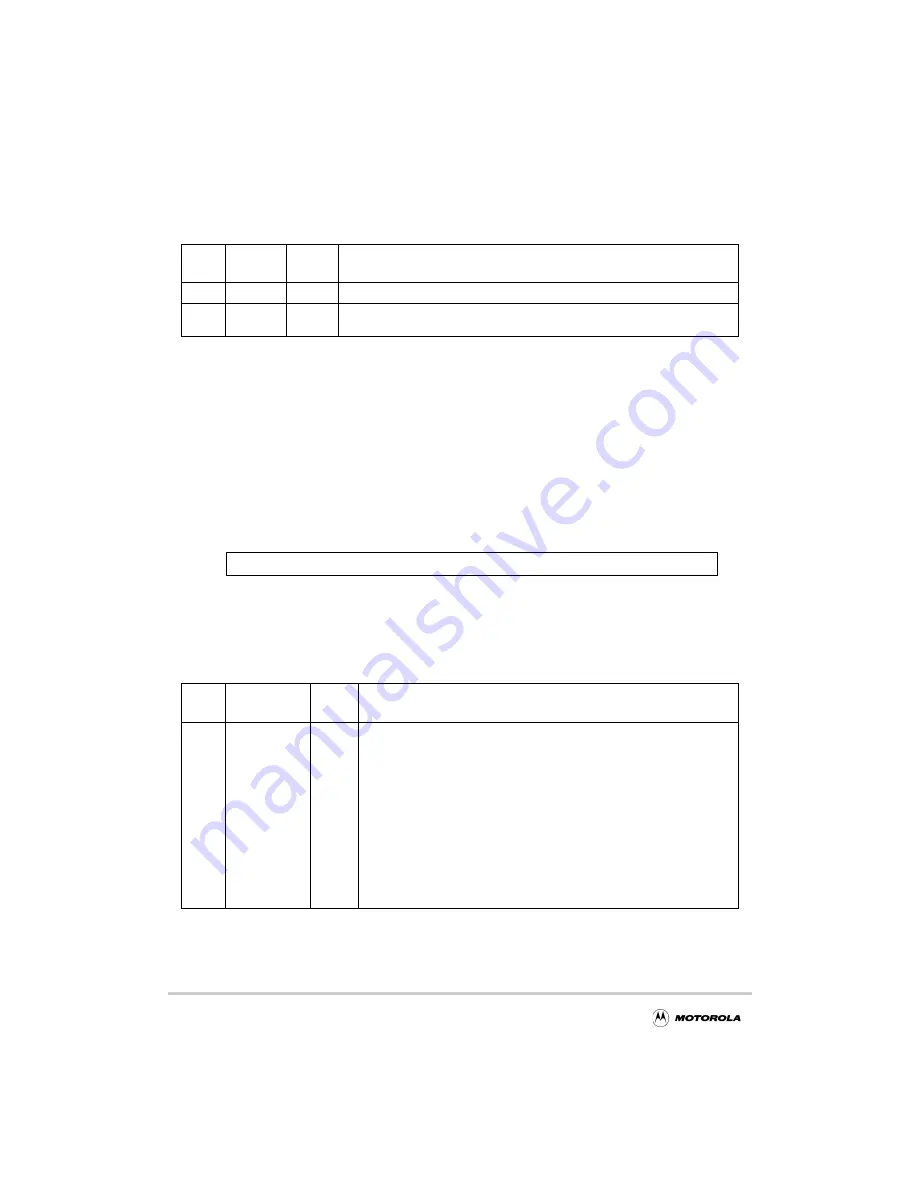

Figure 11-10 shows the bits in the TFRR.

Figure 11-10. Timer Frequency Reporting Register (TFRR)

Table 11-11 describes the bit settings for the TFRR.

Table 11-10. SVR Field Descriptions—Offset 0x4_10E0

Bits

Name

Reset

Value

Description

31–8

—

All 0s

Reserved

7–0

VECTOR

0xFF

Spurious interrupt vector. The vector value in this field is returned when the

interrupt acknowledge register (IACK) is read during a spurious vector fetch.

Table 11-11. TFRR Field Descriptions—Offset 0x4_10F0

Bits

Name

Reset

Value

Description

31–0

TIMER_FREQ

All 0s

Timer frequency. This register is used to report the frequency of the clock

source for the global timers (in ticks/seconds (Hz)) which is always the

SDRAM_CLK signal. The timers operate at 1/8th the speed of the

SDRAM_CLK signal.

The register is only set by software. The value in this register does not affect

the speed of the timers. The timers’ speed is determined by the

PLL_CFG[0–4] signals and the frequency of the PCI_SYNC_IN signal. The

value may be written by the system initialization code after the SDRAM_CLK

frequency has been determined by the firmware. The firmware can use

information stored in the HID1 register and information about the actual

processor frequency to determine the SDRAM_CLK frequency. However, in

some cases, more system frequency information may be required.

TIMER_FREQ

31

0

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...