Chapter 11. Embedded Programmable Interrupt Controller (EPIC) Unit

11-27

Register Definitions

11.9.9 Processor-Related Registers

This section describes the processor-related EPIC registers.

11.9.9.1 Processor Current Task Priority Register (PCTPR)

Software should write the priority of the current processor task in the PCTPR. The EPIC

unit uses this value to compare with the priority of incoming interrupts. The int signal is

asserted to the processor core if the incoming interrupt is not masked, has a greater priority

than that assigned in the PCTPR and ISR, and is greater than the priority of the other

incoming interrupts. Priority levels from 0 (lowest) to 15 (highest) are supported. Setting

the task priority to 15 masks all interrupts to the processor. The PCTPR is initialized to

0x0000_000F when the MPC8240 is reset, or when the P0 bit of the processor initialization

register is set to one. Note that this register is read/write. Figure 11-17 shows the bits of the

PCTPR.

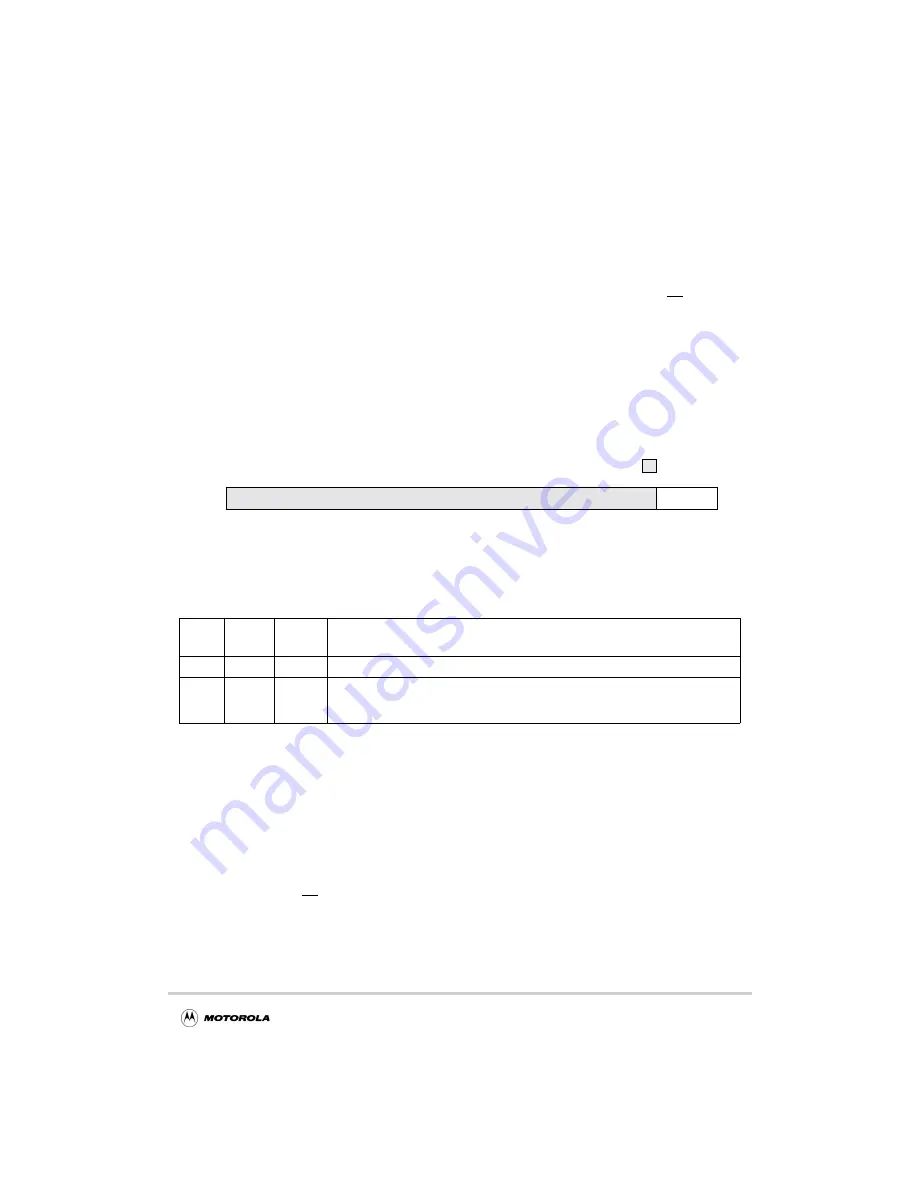

Figure 11-17. Processor Current Task Priority Register (PCTPR)

Table 11-24 shows the bit settings for the PCTPR.

11.9.9.2 Processor Interrupt Acknowledge Register (IACK)

The interrupt acknowledge mechanism on the MPC8240 consists of a read from the

memory-mapped interrupt acknowledge register (IACK) in the EPIC unit. Reading the

IACK returns the interrupt vector corresponding to the highest priority pending interrupt.

Reading IACK also has the following side effects:

•

The associated bit in the IPR is cleared (if it is configured as edge-sensitive).

•

The ISR is updated.

•

The internal int signal is negated.

Reading IACK when there is no interrupt pending returns the spurious vector value. Note

that this register is read-only.

Table 11-24. PCTPR Field Descriptions—Offset 0x6_0080

Bits

Name

Reset

Value

Description

31–4

—

All 0s

Reserved

3–0

TASKP

0xF

Task priority. This field is set 0 to 15, where 15 corresponds to the highest priority for

processor tasks. When PCTPR[TASKP] = 0xF, no interrupts will be signalled to the

processor.

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

TASKP

31

4

3

0

Reserved

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...