12-12

MPC8240 Integrated Processor User’s Manual

Internal Arbitration

The arbitration boundaries for access to the processor/memory data bus shown in

Table 12-2 occur on a cache-line basis. Thus, after every cache line is transferred, requests

for access to the processor/memory bus are ranked by the priorities shown in the table.

Note that the first access of a multi-cache-line read (generated by a PCI master or the DMA

unit) is classified as a PCI read in the table. If snooping is enabled, subsequent reads in

multi-cache-line accesses are classified as speculative PCI reads in the table (with a priority

of 10) until the snoop completes. When the snoop completes, the access changes to a

priority of 2. If snooping is disabled, the subsequent reads in multi-cache-line accesses are

classified as speculative PCI reads with a priority of 2.

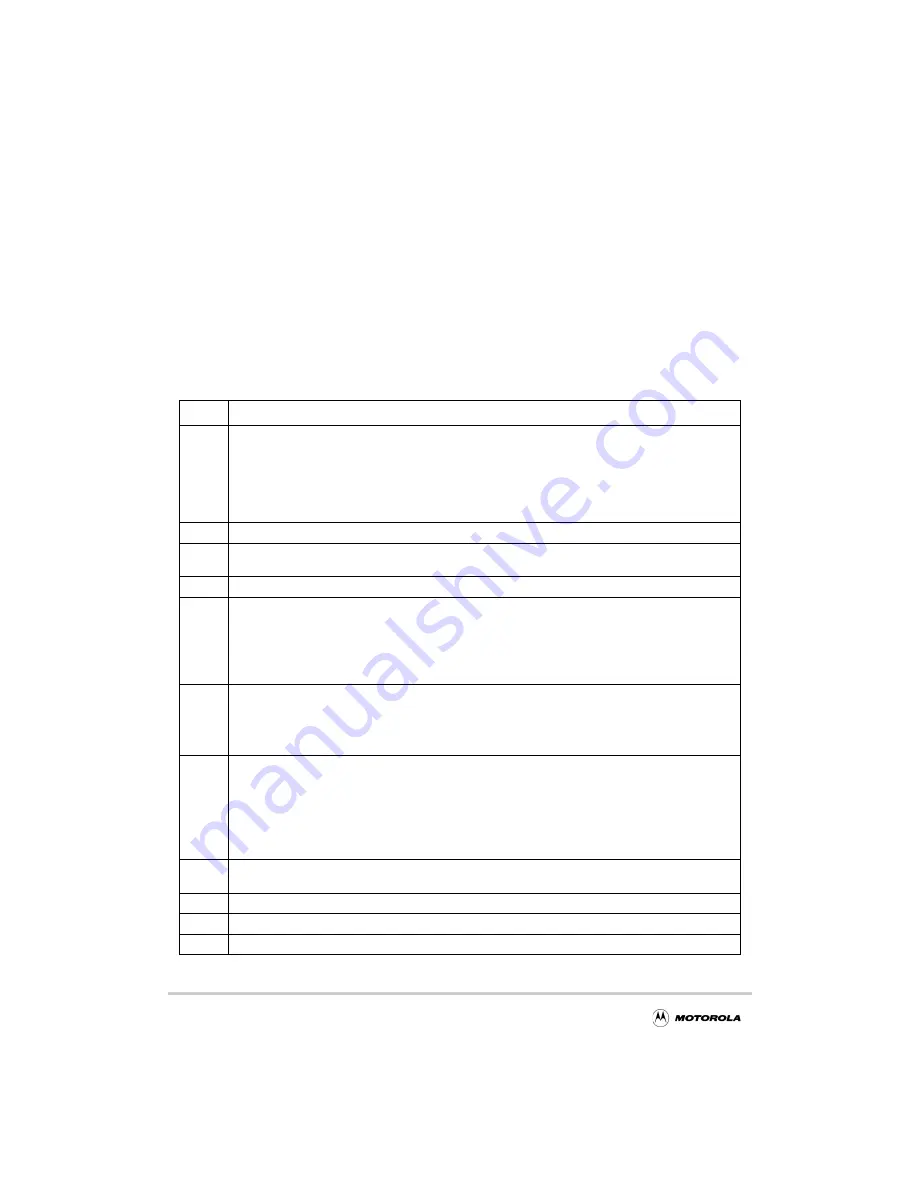

Table 12-2. Internal Arbitration Priorities

Priority

Operation

1

A high-priority copyback buffer flush due to one of the following:

A PCI access to local memory hits in the copyback buffer.

A processor burst write to local memory with ECC enabled hits an address in the PCMWB (with snoop

not complete).

A processor burst write to local memory with ECC enabled hits an address in the PCMRB (with snoop

not complete).

1.5

Pipelined processor reads or writes to local memory (only occurs when snooping is disabled).

2

A PCI read or speculative PCI read from local memory with snoop complete (or snooping disabled). See

Section 12.2.3, “Guaranteeing Minimum PCI Access Latency to Local Memory.”

3

A processor read from local memory

4

A high priority PCMWB flush due to one of the following:

A PCI read hits in the PCMWB.

The PCMWB is full and another PCI write to local memory starts.

A processor to local memory read hits in the PCMWB.

A processor to local memory single-beat write hits in the PCMWB.

5

A medium priority copyback buffer flush due to one of the following:

A processor read hits in the copyback buffer.

A processor single-beat write hits in the copyback buffer.

The copyback buffer is full and new data needs to be written to it.

6

Normal processor transfers including the following:

A processor write to local memory

A snoop copyback due to a PCI write snoop

A processor read from PCI

A processor write to PCI

A copyback buffer fill

7

A PCI read from local memory with snoop not complete. See Section 12.2.3, “Guaranteeing Minimum PCI

Access Latency to Local Memory.”

8

A low-priority copyback buffer flush

9

A low-priority PCMWB flush

10

A PCMRB prefetch from local memory due to a speculative PCI read operation

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...