15-8

MPC8240 Integrated Processor User’s Manual

Memory Interface Valid (MIV)

15.3.5 Debug Address Timing

For examples of debug address timing for various memory types, see Figure 15-8 through

Figure 15-16.

15.4 Memory Interface Valid (MIV)

The memory interface valid signal MIV is asserted whenever FPM, EDO, SDRAM, Flash,

or ROM addresses or data are present on the external memory bus. It is intended to help

reduce the number of bus cycles that logic analyzers must store in memory during a debug

trace and is described in Table 15-7. The MIV signal should be sampled with the rising edge

of SDRAM_CLK[0:3].

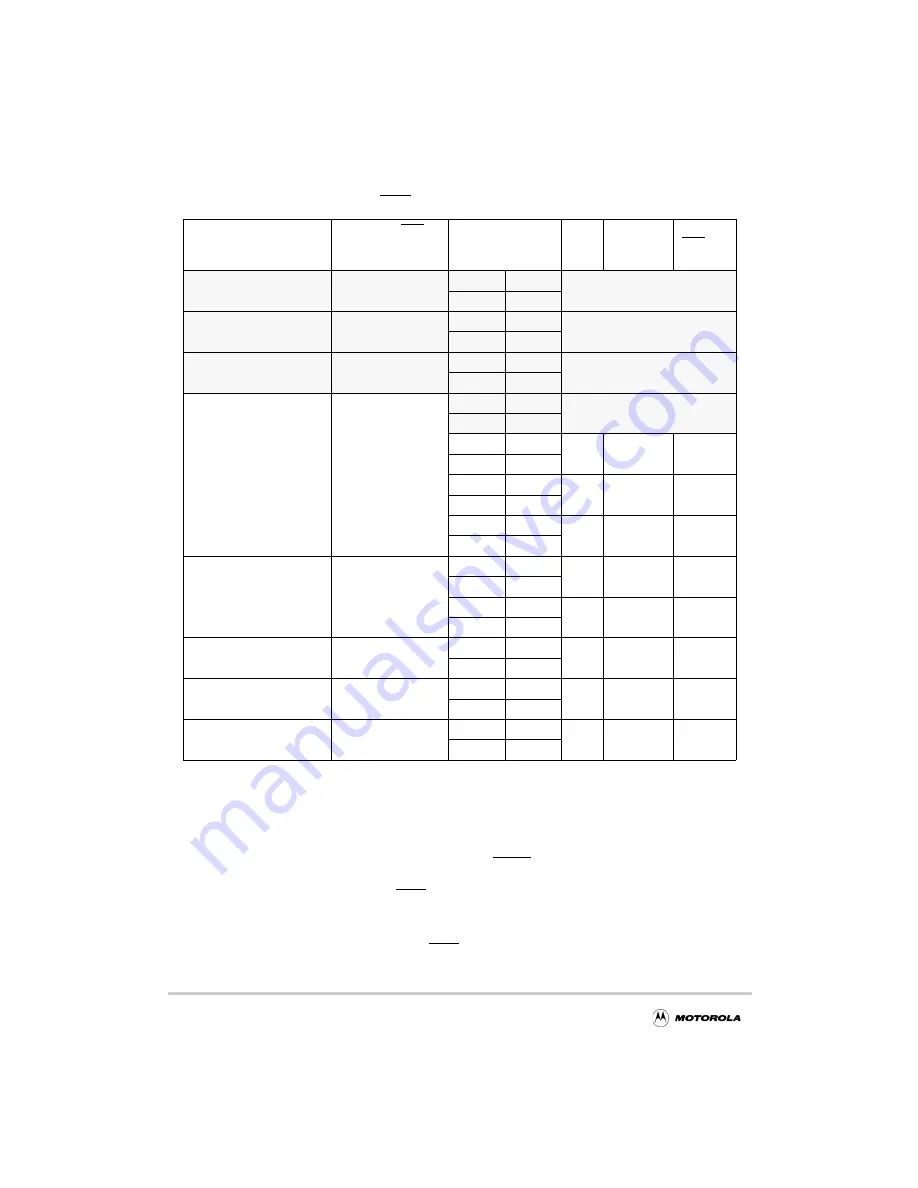

Table 15-6. Example of RAS Encoding For 568-Mbyte Memory System

Partition

Encoded RAS:

Physical

Address [29–27]

Address

Bank

Bank Size

RAS[0:7]

Eighth 128-Mbyte partition of

1 Gbyte main memory

0b111

Ending

0x3FF

undefined

Starting

0x380

Seventh 128-Mbyte partition

of 1 Gbyte main memory

0b110

Ending

0x37F

undefined

Starting

0x300

Sixth 128-Mbyte partition of

1 Gbyte main memory

0b101

Ending

0x2FF

undefined

Starting

0x280

Fifth 128-Mbyte partition of

1Gbyte main memory

0b100

Ending

0x27F

undefined

Starting

0x238

Ending

0x237

7

8 MBytes

0xFE

Starting

0x230

Ending

0x22F

6

16 MBytes

0xFD

Starting

0x220

Ending

0x21F

5

32 MBytes

0xFB

Starting

0x200

Fourth 128-Mbyte partition

of 1 Gbyte main memory

0b011

Ending

0x1FF

4

64 MBytes

0xF7

Starting

0x1C0

Ending

0x1BF

3

64 MBytes

0xEF

Starting

0x180

Third 128-Mbyte partition of

1 Gbyte main memory

0b010

Ending

0x17F

1

128 MBytes

0xBF

Starting

0x100

Second 128-Mbyte partition

of 1 Gbyte main memory

0b001

Ending

0x0FF

2

128 MBytes

0xDF

Starting

0x080

First 128-Mbyte partition of 1

Gbyte main memory

0b000

Ending

0x07F

0

128 MBytes

0x7F

Starting

0x000

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...