Chapter 16. Programmable I/O and Watchpoint

16-7

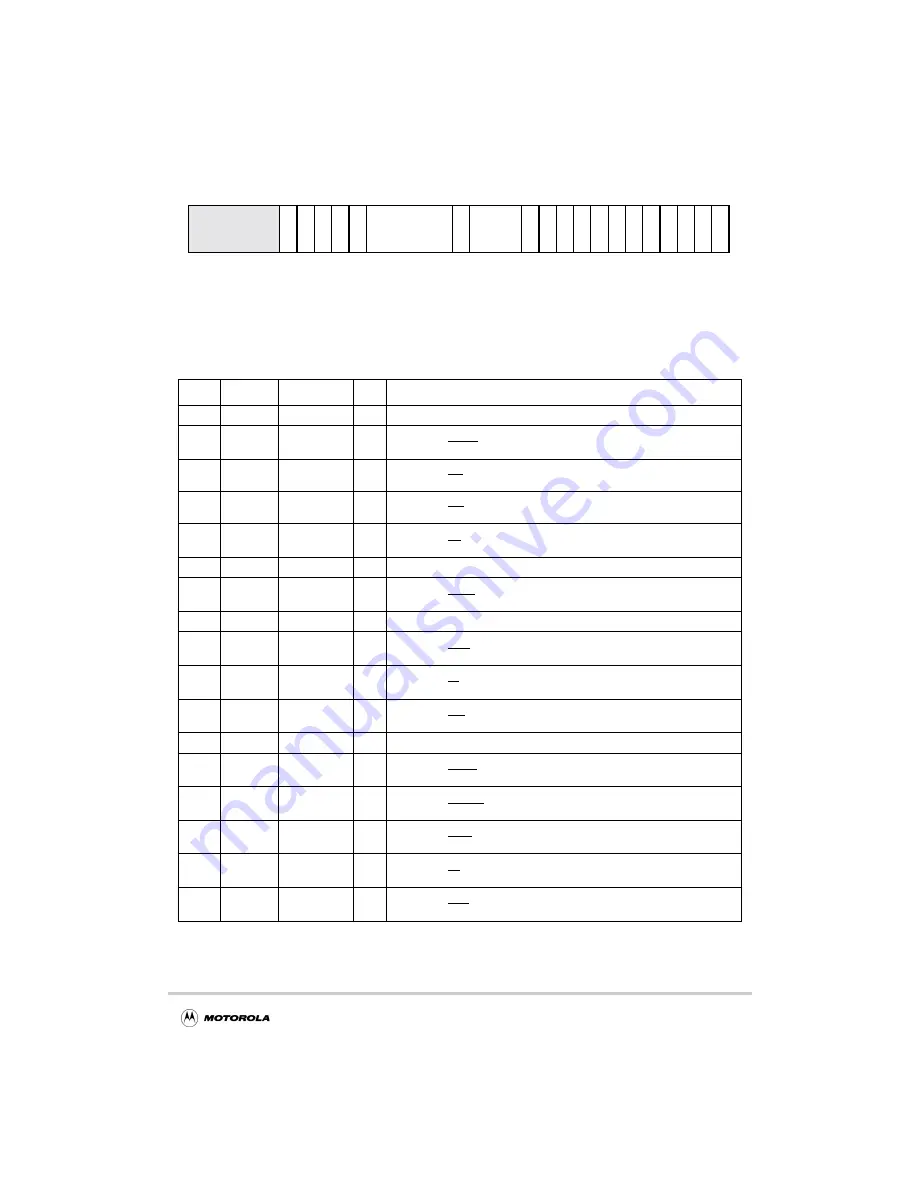

Watchpoint Registers

Figure 16-8. Watchpoint #2 Control Mask Register (WP2_CNTL_MASK)—

Offsets 0xF_F038, 0xF38

Table 16-5 shows the bit definitions for WP1_CNTL_MASK and WP2_CNTL_MASK.

Table 16-5. Watchpoint Control Mask Register Bit Field Definitions

Bits

Name

Reset Value

R/W

Description

31–25

—

0b000_000

R

Reserved

24

QACK_

0

R/W

0 Ignore QACK_ trigger bit in WPx_CNTL_TRIG.

1 Compare QACK on peripheral logic bus with WPx_CNTL_TRIG bit.

23

BR_

0

RW

0 Ignore BR_ trigger bit in WPx_CNTL_TRIG

1 Compare BR on peripheral logic bus with WPx_CNTL_TRIG bit

22

BG_

0

RW

0 Ignore BG_ trigger bit in WPx_CNTL_TRIG

1 Compare BG on peripheral logic bus with WPx_CNTL_TRIG bit

21

TS_

0

R/W

0 Ignore TS_ trigger bit in WPx_CNTL_TRIG.

1 Compare TS on peripheral logic bus with WPx_CNTL_TRIG bit.

20–16

TT[0:4]

0b0_0000

R/W

Trigger mask for peripheral logic address transfer attribute

15

TBST_

0

R/W

0 Ignore TBST_ trigger bit in WPx_CNTL_TRIG.

1 Compare TBST on peripheral logic bus with WPx_CNTL_TRIG bit.

14–12

TSIZ[0:2]

0b000

R/W

Trigger mask for peripheral logic transfer size

11

GBL_

0

R/W

0 Ignore GBL_ trigger bit in WPx_CNTL_TRIG,

1 Compare GBL on peripheral logic bus with WPx_CNTL_TRIG bit.

10

CI_

0

R/W

0 Ignore CI_ trigger bit in WPx_CNTL_TRIG.

1 Compare CI on peripheral logic bus with WPx_CNTL_TRIG bit.

9

WT_

0

R/W

0 Ignore WT_ trigger bit in WPx_CNTL_TRIG.

1 Compare WT on peripheral logic bus with WPx_CNTL_TRIG bit.

8–7

TC[0:1]

0b00

RW

Trigger mask for peripheral logic Transfer Code

6

AACK_

0

R/W

0 Ignore AACK_ trigger bit in WPx_CNTL_TRIG.

1 Compare AACK on peripheral logic bus with WPx_CNTL_TRIG bit.

5

ARTRY_

0

R/W

0 Ignore ARTRY_ trigger bit in WPx_CNTL_TRIG.

1 Compare ARTRY on peripheral logic bus with WPx_CNTL_TRIG bit.

4

DBG_

0

R/W

0 Ignore DBG_ trigger bit in WPx_CNTL_TRIG.

1 Compare DBG on peripheral logic bus with WPx_CNTL_TRIG bit.

3

TA_

0

R/W

0 Ignore TA_ trigger bit in WPx_CNTL_TRIG.

1 Compare TA on peripheral logic bus with WPx_CNTL_TRIG bit.

2

TEA_

0

R/W

0 Ignore TEA_ trigger bit in WPx_CNTL_TRIG.

1 Compare TEA on peripheral logic bus with WPx_CNTL_TRIG bit.

0000_00

QREQ_

QA

CK_

BR_

BG_

TS_

TT0[0:4]

TBST_

TSIZ[0:2]

GBL_

CI_

WT_

TC0

TC1

AA

CK_

AR

TR

Y_

DBG_

TA

_

TEA_

INT_

MCP_

31

26 25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...