E-6

MPC8240 Integrated Processor User’s Manual

PowerPC Register Set

E.1.1.4 Floating-Point Status and Control Register (FPSCR)

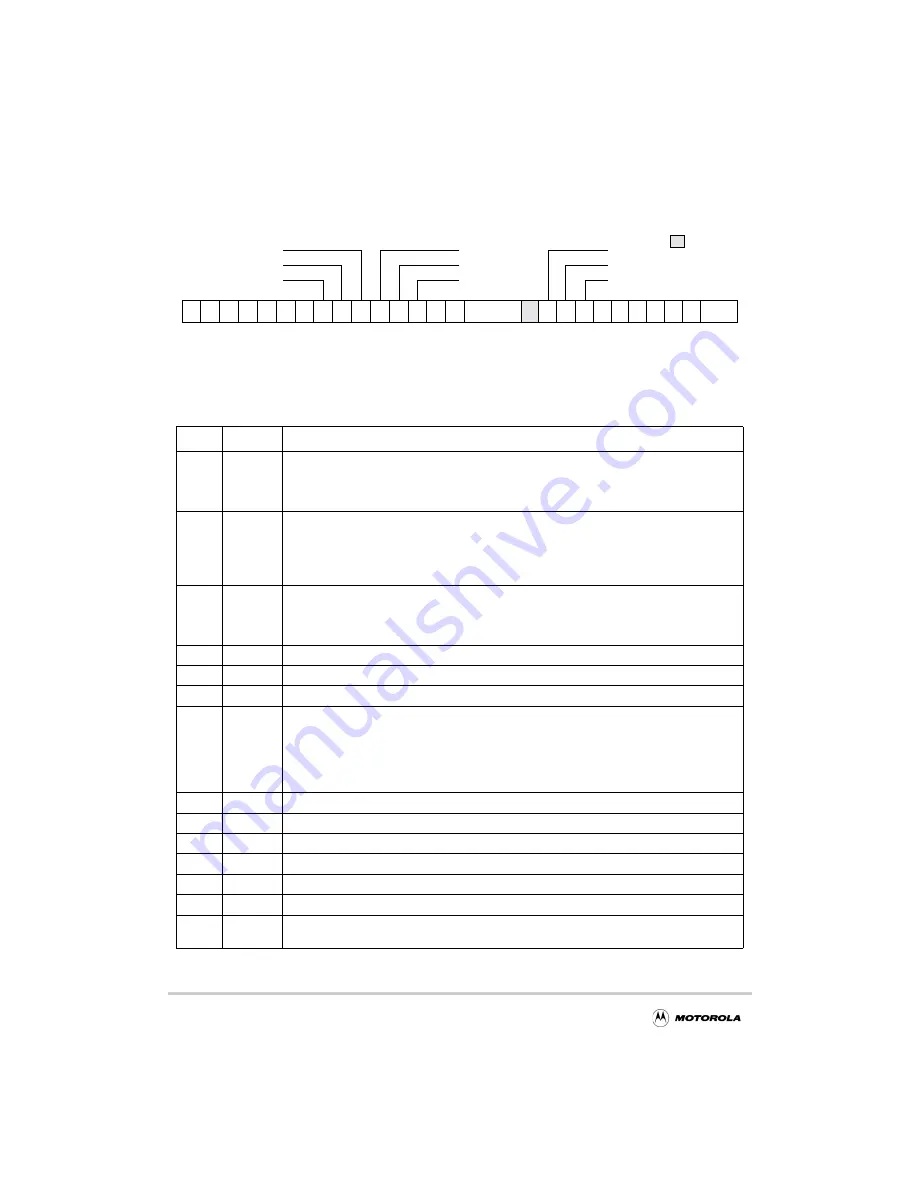

The FPSCR is shown in Figure E-5.

Figure E-5. Floating-Point Status and Control Register (FPSCR)

A listing of FPSCR bit settings is shown in Table E-4.

Table E-4. FPSCR Bit Settings

Bit(s)

Name

Description

0

FX

Floating-point exception summary. Every floating-point instruction, except mtfsfi and mtfsf,

implicitly sets FPSCR[FX] if that instruction causes any of the floating-point exception bits in the

FPSCR to transition from 0 to 1. The mcrfs, mtfsfi, mtfsf, mtfsb0, and mtfsb1 instructions can

alter FPSCR[FX] explicitly. This is a sticky bit.

1

FEX

Floating-point enabled exception summary. This bit signals the occurrence of any of the

enabled exception conditions. It is the logical OR of all the floating-point exception bits masked

by their respective enable bits (FEX = (VX & VE) ^ (OX & OE) ^ (UX & UE) ^ (ZX & ZE) ^ (XX &

XE)). The mcrfs, mtfsf, mtfsfi, mtfsb0, and mtfsb1 instructions cannot alter FPSCR[FEX]

explicitly. This is not a sticky bit.

2

VX

Floating-point invalid operation exception summary. This bit signals the occurrence of any

invalid operation exception. It is the logical OR of all of the invalid operation exceptions. The

mcrfs, mtfsf, mtfsfi, mtfsb0, and mtfsb1 instructions cannot alter FPSCR[VX] explicitly. This

is not a sticky bit.

3

OX

Floating-point overflow exception. This is a sticky bit.

4

UX

Floating-point underflow exception. This is a sticky bit.

5

ZX

Floating-point zero divide exception. This is a sticky bit.

6

XX

Floating-point inexact exception. This is a sticky bit.

FPSCR[XX] is the sticky version of FPSCR[FI]. The following rules describe how FPSCR[XX] is

set by a given instruction:

• If the instruction affects FPSCR[FI], the new value of FPSCR[XX] is obtained by logically

ORing the old value of FPSCR[XX] with the new value of FPSCR[FI].

• If the instruction does not affect FPSCR[FI], the value of FPSCR[XX] is unchanged.

7

VXSNAN

Floating-point invalid operation exception for SNaN. This is a sticky bit.

8

VXISI

Floating-point invalid operation exception for

∞

–

∞

. This is a sticky bit.

9

VXIDI

Floating-point invalid operation exception for

∞

÷

∞

. This is a sticky bit.

10

VXZDZ

Floating-point invalid operation exception for 0 ÷ 0. This is a sticky bit.

11

VXIMZ

Floating-point invalid operation exception for

∞

* 0. This is a sticky bit.

12

VXVC

Floating-point invalid operation exception for invalid compare. This is a sticky bit.

13

FR

Floating-point fraction rounded. The last arithmetic or rounding and conversion instruction that

rounded the intermediate result incremented the fraction. This bit is not sticky.

0

1

2

3

4

5

6

7

8

9

10 11

12 13 14 15

19 20 21 22 23 24 25 26 27 28 29 30

31

VXIDI

VXISI

VXSNAN

VXZDZ

VXIMZ

VXVC

VXSOFT

VXSQRT

VXCVI

Reserved

FX FEX VX OX UX ZX XX

FR FI

FPRF

0 VE OE UE ZE XE NI

RN

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...