MOTOROLA

Chapter 6. External Signals

6-3

Part III. The Hardware Interface

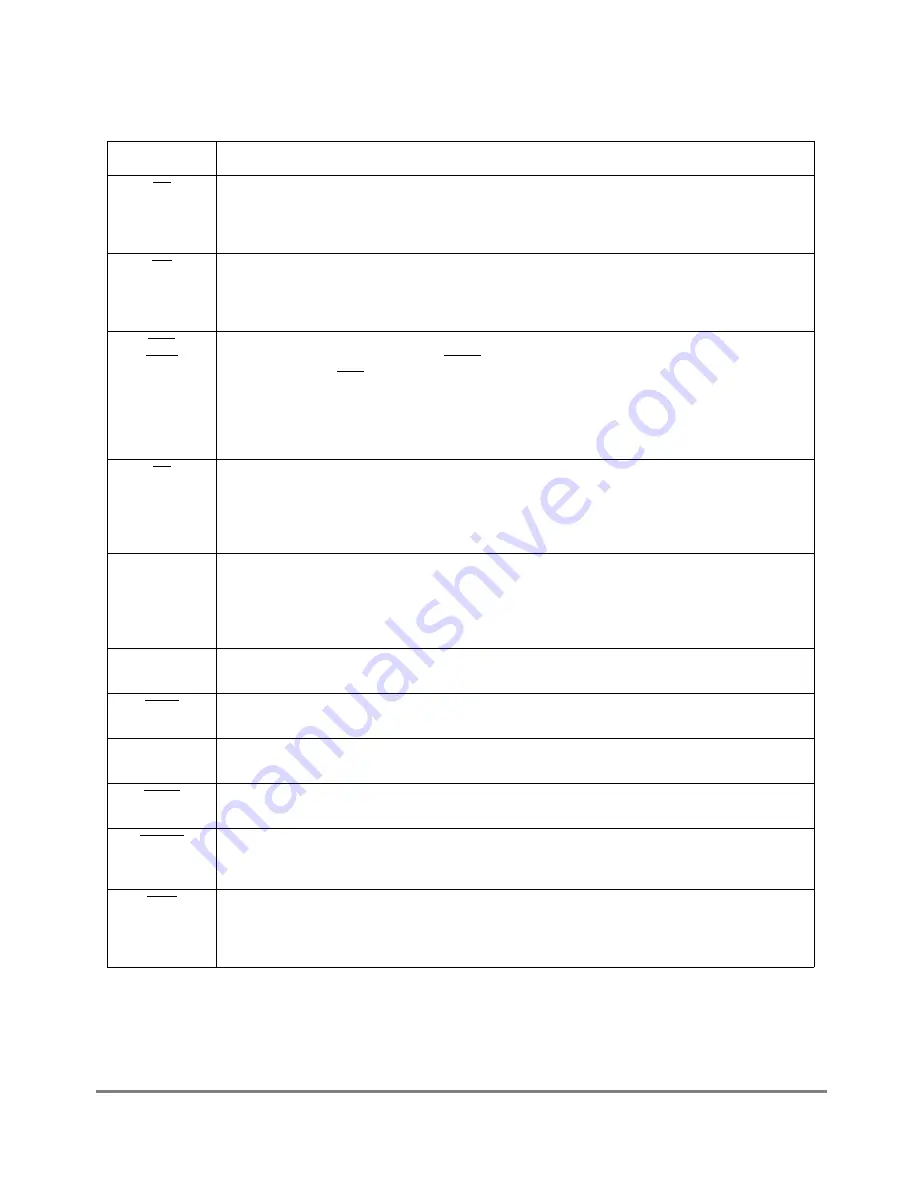

Table 6-1. External Signals

Signal Description

BR

60x bus requestÑThis is an output when an external arbiter is used and an input when an internal

arbiter is used. As an output the MPC8260 asserts this pin to request ownership of the 60x bus. As

an input an external master should assert this pin to request 60x bus ownership from the internal

arbiter.

BG

60x bus grantÑThis is an output when an internal arbiter is used and an input when an external

arbiter is used. As an output the MPC8260 asserts this pin to grant 60x bus ownership to an

external bus master. As an input the external arbiter should assert this pin to grant 60x bus

ownership to the MPC8260.

ABB

IRQ2

60x address bus busyÑ(Input/output)As an output the MPC8260 asserts this pin for the duration of

the address bus tenure. Following an AACK, which terminates the address bus tenure, the

MPC8260 negates ABB for a fraction of a bus cycle and than stops driving this pin. As an input the

MPC8260 will not assume 60x bus ownership as long as it senses this pin is asserted by an

external 60x bus master.

Interrupt Request 2ÑThis input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

TS

60x bus transfer startÑ(Input/output)Assertion of this pin signals the beginning of a new address

bus tenure. The MPC8260 asserts this signal when one of its internal 60x bus masters (core, DMA,

PCI bridge) begins an address tenure. When the MPC8260 senses this pin being asserted by an

external 60x bus master, it will respond to the address bus tenure as required (snoop if enabled,

access internal MPC8260 resources, memory controller support).

A[0Ð31]

60x address busÑThese are input/output pins. When the MPC8260 is in external master bus

mode, these pins function as the 60x address bus. The MPC8260 drives the address of its internal

60x bus masters and respond to addresses generated by external 60x bus masters. When the

MPC8260 is in internal master bus mode, these pins are used as address lines connected to

memory devices and controlled by the MPC8260Õs memory controller.

TT[0Ð4]

60x bus transfer typeÑThese are input/output pins. The 60x bus master drives these pins during

the address tenure to specify the type of the transaction.

TBST

60x bus transfer burstÑ(Input/output)The 60x bus master asserts this pin to indicate that the

current transaction is a burst transaction (transfers 4 double words).

TSIZ[0Ð3]

60x transfer sizeÑThese are input/output pins. The 60x bus master drives these pins with a value

indicating the amount of bytes transferred in the current transaction.

AACK

60x address acknowledgeÑThis is an input/output signal. A 60x bus slave asserts this signal to

indicate that it identiÞed the address tenure. Assertion of this signal terminates the address tenure.

ARTRY

60x address retryÑ(Input/output)Assertion of this signal indicates that the bus transaction should

be retried by the 60x bus master. The MPC8260 asserts this signal to enforce data coherency with

its internal cache and to prevent deadlock situations.

DBG

60x data bus grantÑThis is an output when an internal arbiter is used and an input when an

external arbiter is used. As an output the MPC8260 asserts this pin to grant 60x data bus

ownership to an external bus master. As an input the external arbiter should assert this pin to grant

60x data bus ownership to the MPC8260.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......