10-8

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part III. The Hardware Interface

selected according to the type of external access transacted. At every clock cycle, the

logical value of the external signals speciÞed in the RAM array is output on the

corresponding UPM pins.

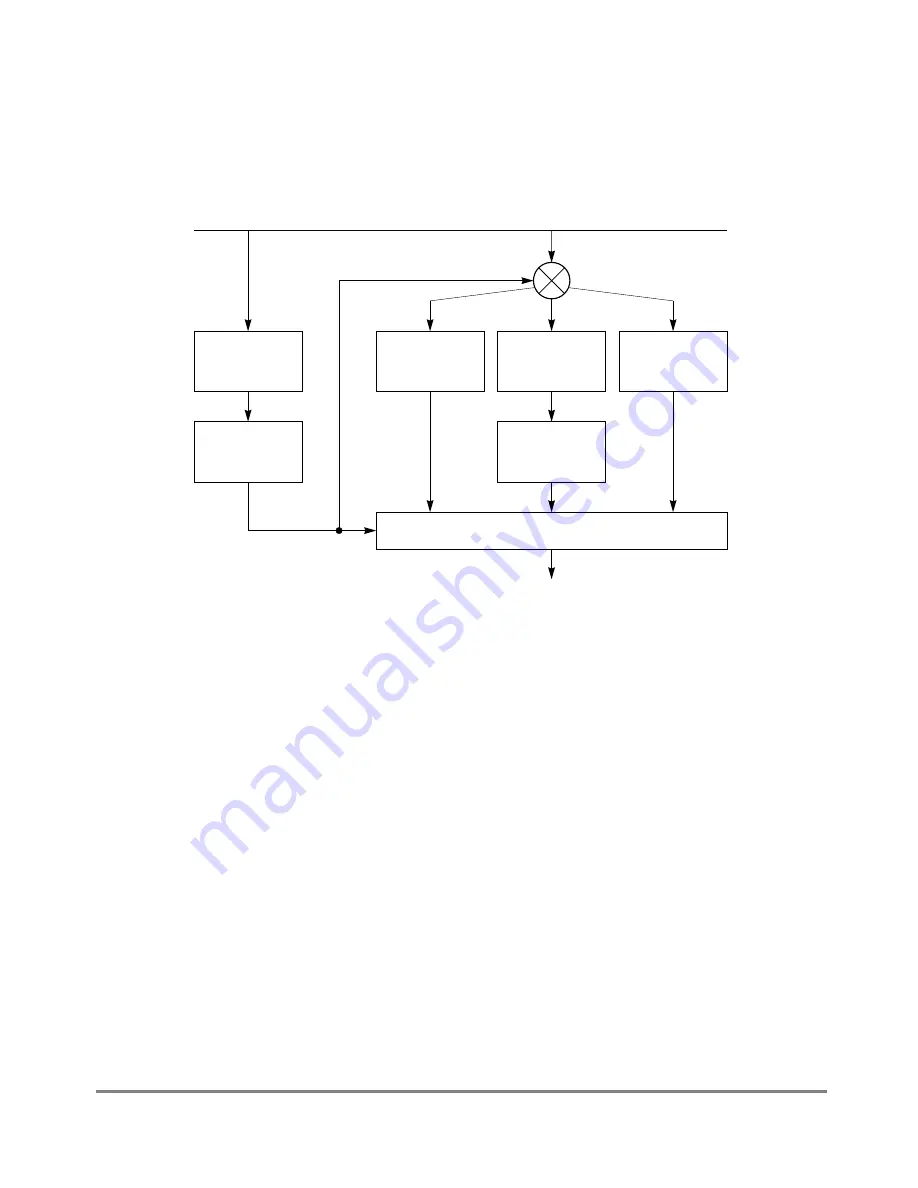

Figure 10-4 shows a basic conÞguration.

Figure 10-4. Basic Memory Controller Operation

The SDRAM mode registers (LSDMR and PSDMR) deÞne the global parameters for the

60x and local SDRAM devices. Machine A/B/C mode registers (MxMR) deÞne most of the

global features for each UPM. GPCM parameters are deÞned in the option register (ORx).

Some SDRAM and UPM parameters are also deÞned in ORx.

10.2.1 Address and Address Space Checking

The deÞned base address is written to the BR

x

. The bank size is written to the OR

x

. Each

time a bus cycle access is requested on the 60x or local bus, addresses are compared with

each bank. If a match is found on a memory controller bank, the attributes deÞned in the

BR

x

and OR

x

for that bank are used to control the memory access. If a match is found in

more than one bank, the lowest-numbered bank handles the memory access (that is, bank 0

has priority over bank 1).

Note that although 60x bus accesses that hit a bank allocated to the local bus are transferred

to the local bus, local bus access hits to banks allocated to the 60x bus are ignored.

60x-to-local bus transactions has priority over regular memory bank hits.

Address

Comparator

Bank Select

UPMx

GPCM

MS/BS

Fields

Signals

Timing

Generator

MUX

Internal/External Memory Access Request Select

Address (A),

Address

Type (AT)

External Signals

SDRAM Machine

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......