MOTOROLA

Chapter 10. Memory Controller

10-35

Part III. The Hardware Interface

10.4.1 Supported SDRAM ConÞgurations

The MPC8260 memory controller supports any SDRAM conÞguration under the

restrictions that all SDRAM devices that reside on the same bus (60x or local) should have

the same port size and timing parameters.

10.4.2 SDRAM Power-On Initialization

At system reset, initialization software must set up the programmable parameters in the

memory controller banks registers (OR

x

, BR

x

, P/LSDMR). After all memory parameters

are conÞgured, system software should execute the following initialization sequence for

each SDRAM device.

1. Issue a

PRECHARGE

-

ALL

-

BANKS

command

2. Issue eight

CBR

REFRESH

commands

3. Issue a

MODE

-

SET

command to initialize the mode register

The initial commands are executed by setting P/LSDMR[OP] and accessing the SDRAM

with a single-byte transaction. See Figure 10-10.

Note that software should ensure that no memory operations begin until this process

completes.

10.4.3 JEDEC-Standard SDRAM Interface Commands

The MPC8260 performs all accesses to SDRAM by using JEDEC-standard SDRAM

interface commands. The SDRAM device samples the command and data inputs on the

rising edge of the MPC8260 bus clock. Data at the output of the SDRAM device must be

sampled on the rising edge of the MPC8260 bus clock.

The MPC8260 provides the following SDRAM interface commands:

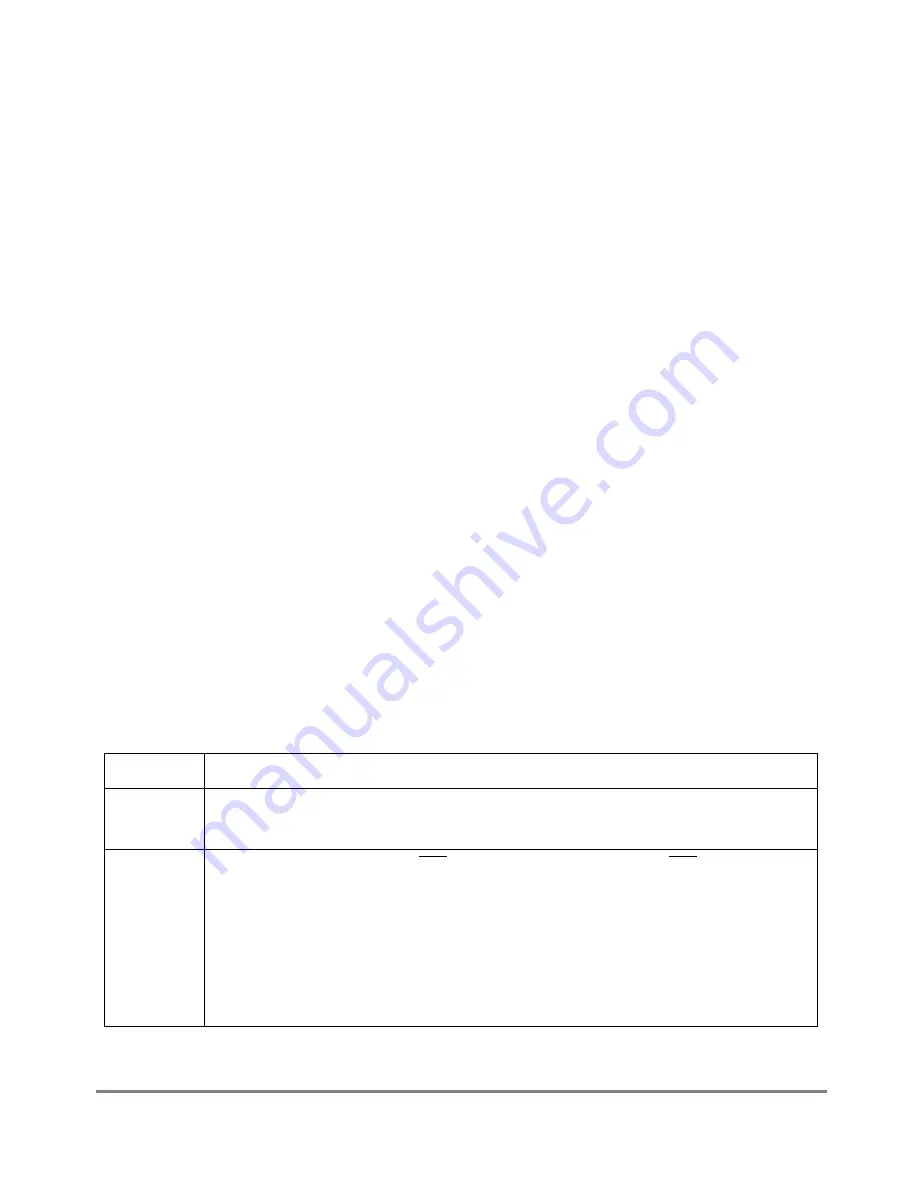

Table 10-18. SDRAM Interface Commands

Command

Description

BANK

-

ACTIVATE

Latches the row address and initiates a memory read of that row. Row data is latched in SDRAM

sense ampliÞers and must be restored with a

PRECHARGE

command before another

BANK

-

ACTIVATE

is

issued.

MODE

-

SET

Allows setting of SDRAM optionsÑCAS latency, burst type, and burst length. CAS latency depends

on the SDRAM device used (some SDRAMs provide CAS latency of 1, 2, or 3; some provide a latency

of 1, 2, 3, or 4, etc.). Burst type must be chosen according to the 60x cache wrap (sequential).

Although some SDRAMs provide burst lengths of 1, 2, 4, 8, or a page, MPC8260 supports only a

4-beat burst for 64-bit port size and an 8-beat burst for 32-bit port size. MPC8260 does not support

burst lengths of 1, 2, and a page for SDRAMs. The mode register data (CAS latency, burst length, and

burst type) is programmed into the P/LSDMR register by initialization software at reset. After the P/

LSDMR is set, the MPC8260 transfers the information in the SDMODE Þeld to the SDRAM array by

issuing a

MODE

-

SET

command. Section 10.4.9, ÒSDRAM Mode-Set Command Timing,Ó gives timing

information.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......