MOTOROLA

Chapter 10. Memory Controller

10-57

Part III. The Hardware Interface

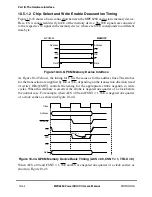

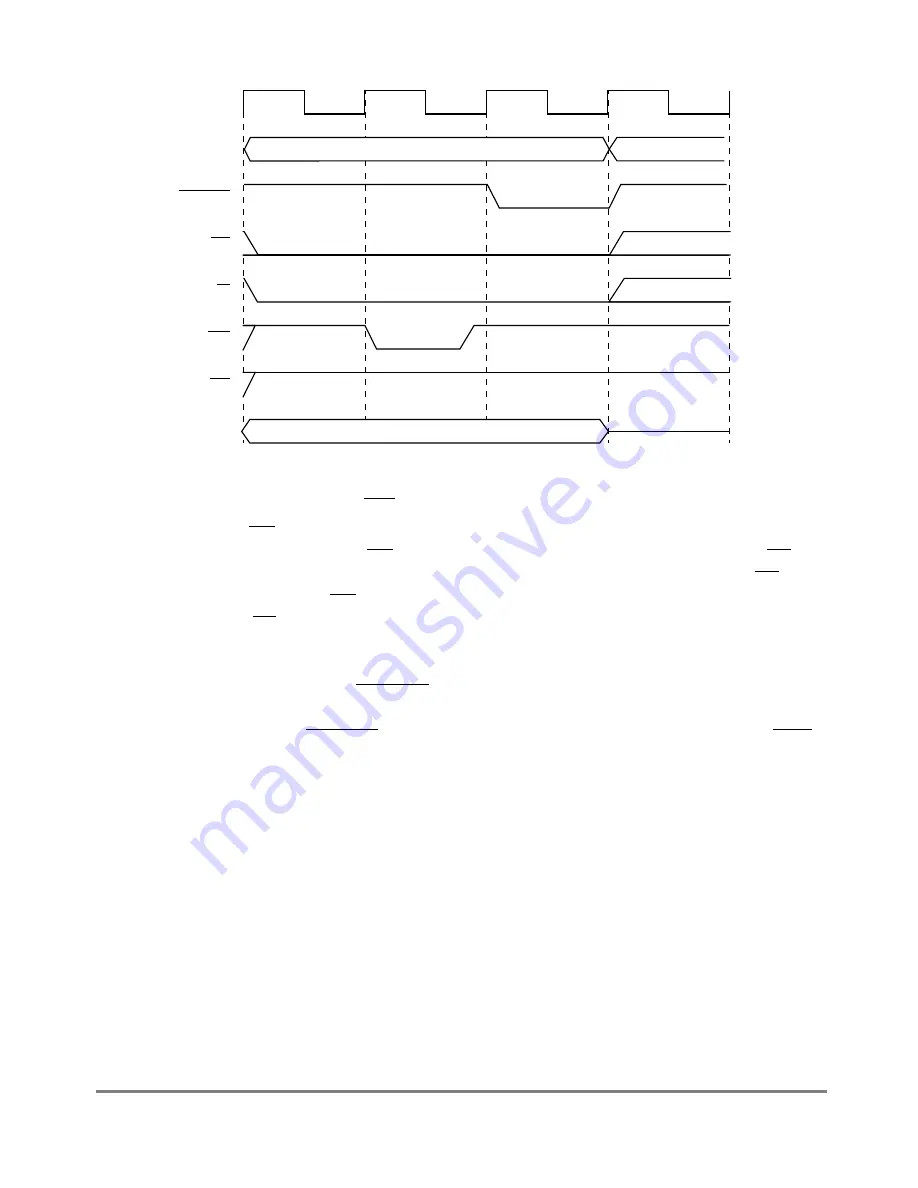

Figure 10-49. GPCM Relaxed-Timing Write (ACS = 00, SCY = 0, CSNT = 1, TRLX = 1)

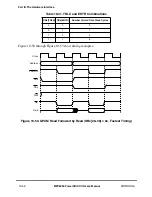

10.5.1.4 Output Enable (OE) Timing

The timing of the OE is affected only by TRLX. It always asserts and negates on the rising

edge of the external bus clock. OE always asserts on the rising clock edge after CS is

asserted, and therefore its assertion can be delayed (along with the assertion of CS) by

programming TRLX = 1. OE deasserts on the rising clock edge coinciding with or

immediately after CS deassertion.

10.5.1.5 Programmable Wait State ConÞguration

The GPCM supports internal PSDVAL generation. It allows fast accesses to external

memory through an internal bus master or a maximum 17-clock access by programming

OR

x

[SCY]. The internal PSDVAL generation mode is enabled if OR

x

[SETA] = 0. If GTA

is asserted externally at least two clock cycles before the wait state counter has expired, the

current memory cycle is terminated. When TRLX = 1, the number of wait states inserted

by the memory controller is deÞned by 2 x SCY or a maximum of 30 wait states.

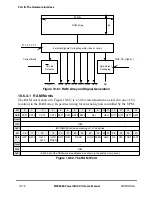

10.5.1.6 Extended Hold Time on Read Accesses

Slow memory devices that take a long time to turn off their data bus drivers on read accesses

should chose some combination of OR

x

[29Ð30] (TRLX and EHTR). Any access following

a read access to the slower memory bank is delayed by the number of clock cycles speciÞed

by Table 10-31. See Figure 10-50 through Figure 10-53 for timing examples.

Clock

Address

PSDVAL

CS

R/W

WE

OE

Data

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......