MOTOROLA

Chapter 18. SDMA Channels and IDMA Emulation

18-7

Part IV. Communications Processor Module

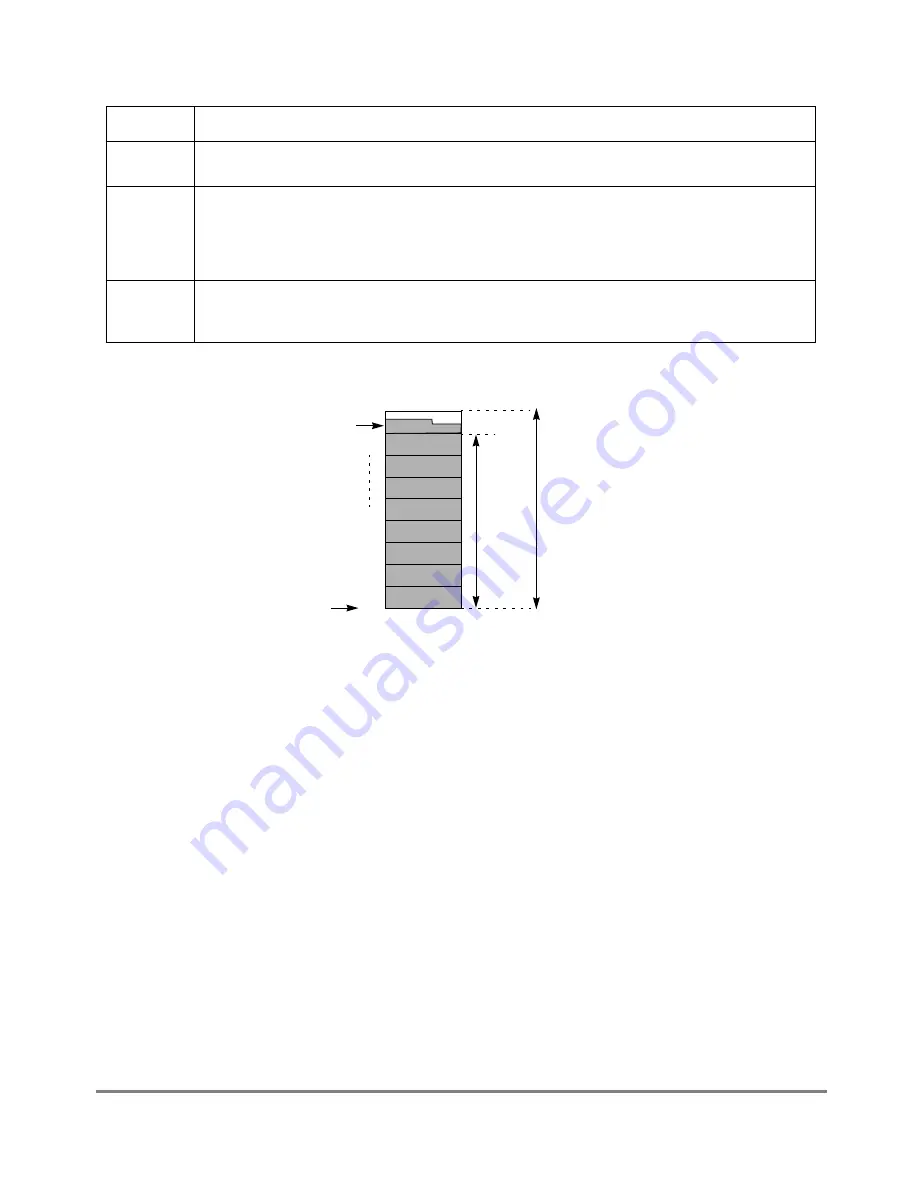

Figure 18-5 shows the IDMA transfer buffer.

Figure 18-5. IDMA Transfer Buffer in the Dual-Port RAM

Each bufferÕs contents are transferred in three phases:

¥

First phase. The internal transfer buffer is Þlled with [EOB

(alignment to source address)

+

SS_MAX] bytes, read from the source bus. Then, if EOB

(alignment to destination address)

£

EOB

(alignment to source address)

, [EOB

(destination)

+ SS_MAX] bytes are written from the

transfer buffer to the destination bus; or if EOB

(destination)

> EOB

(source)

,

[EOB

(destination)

+ (k-2)*32] bytes are written bytes are written. This write transfer

size leaves a remainder of 0Ð31 bytes in the transfer buffer after the last write burst

of the steady-state phase. After the Þrst phase, burst alignment is ensured.

¥

Steady-state phase. The transfer buffer is Þlled with SS_MAX bytes (k-1 bursts),

read from the source bus in STS units. Then, SS_MAX bytes are written to the

destination bus, in DTS units, from the transfer buffer. Because alignment is ensured

from Þrst phase, all bus transfers are bursts. This sequence is repeated until there are

no more than SS_MAX bytes to be transferred. A remainder of 0Ð31 bytes is left in

the transfer buffer after the last burst write.

Table 18-3. IDMA Transfer Parameters

Parameter

Description

DMA_WRAP Determines the size of the dedicated IDMA transfer buffer in dual-port RAM. The buffer size is a

multiple of a 60x burst size (k*32 bytes).

SS_MAX

Initialized to (IDMA_transfer_buffer_size - 32) bytes, which is the steady-state maximum transfer size of

IDMA transfer. This condition ensures that the transfer buffer is either Þlled by one SS_MAX bytes

transfer and emptied in one or several transfers, or Þlled by one or several transfers to be emptied in

one SS_MAX bytes transfer. In terms of bursts, if the transfer buffer contains k bursts (each is 32 bytes

long), then SS_MAX equals to k-1 bursts which is (k-1)*32 bytes.

STS/DTS

Source/destination transfer size. These parameters determine the access sizes in which the source/

destination is accessed in steady state of work. At least one of these values (DTS/STS) must be

initialized to the value of SS_MAX.

SS_MAX

DMA_WRAP determines IDMA transfer buffer size

EOB[0–31]

32

64

96

0

128

(k-1)*32

(32 * k) bytes

Base Address (aligned to buffer size)

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......