19-16

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

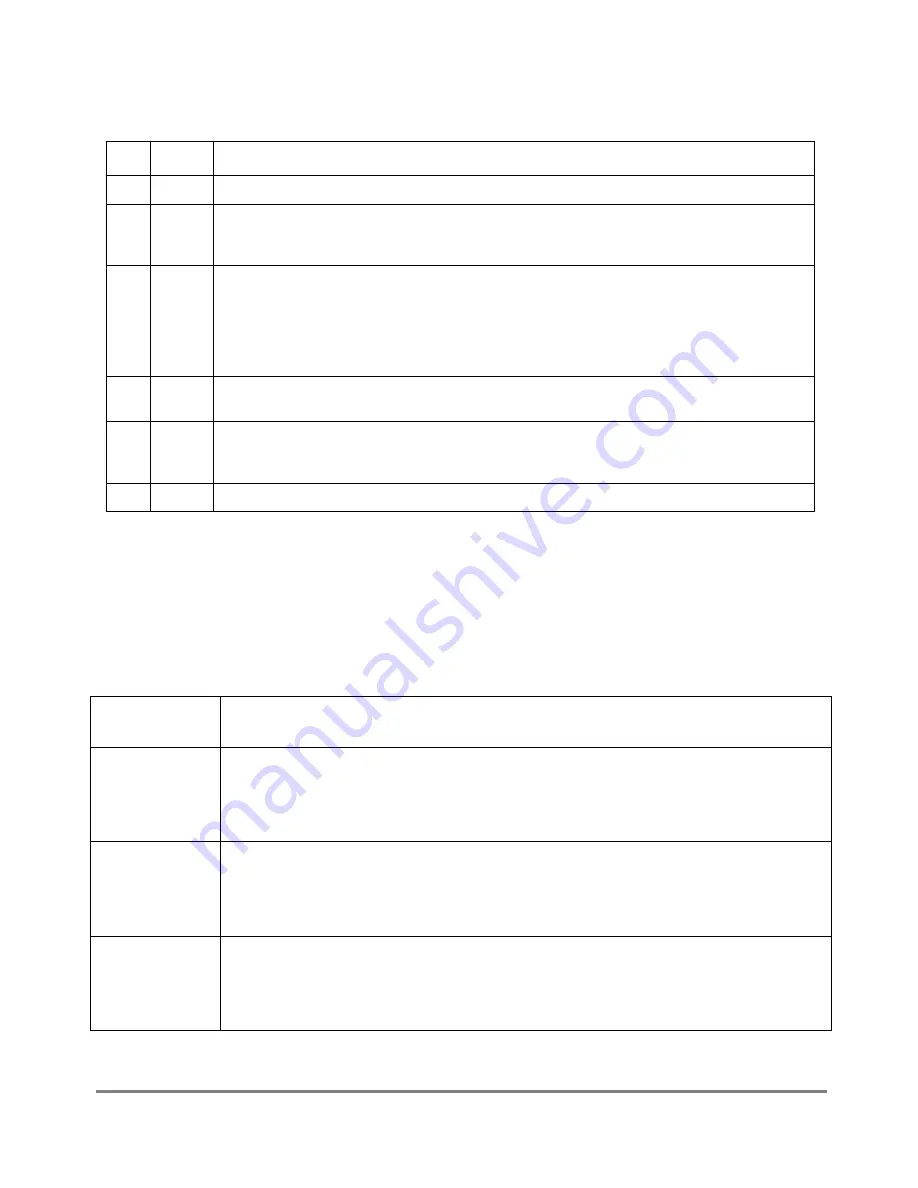

Table 19-6 describes RFCR

x

/TFCR

x

Þelds.

19.3.3 Handling SCC Interrupts

To allow interrupt handling for SCC-speciÞc events, event, mask, and status registers are

provided within each SCCÕs internal memory map area; see Table 19-7. Because interrupt

events are protocol-dependent, event descriptions are found in the speciÞc protocol

chapters.

Table 19-6. RFCR

x

/TFCR

x

Field Descriptions

Bits

Name

Description

0Ð1

Ñ

Reserved, should be cleared.

2

GBL

Global

0 Snooping disabled.

1 Snooping enabled.

3Ð4

BO

Byte ordering. Set BO to select the required byte ordering for the buffer. If BO is changed on-the-ßy,

it takes effect at the beginning of the next frame (Ethernet, HDLC, and transparent) or at the

beginning of the next BD.

00 Reserved

01 PowerPC little-endian.

1x Big-endian or true little-endian.

5

TC2

Transfer code. Contains the transfer code value of TC[2], used during this SDMA channel memory

access. TC[0Ð1] is driven with a 0b11 to identify this SDMA channel access as a DMA-type access.

6

DTB

Data bus indicator

0 Use 60x bus for SDMA operation

1 Use local bus for SDMA operation

7

Ñ

Reserved, should be cleared.

Table 19-7. SCC

x

Event, Mask, and Status Registers

Register &

IMMR Offset

Description

SCCE

x

0x11A10 (SCCE1);

0x11A30 (SCCE2);

0x11A50 (SCCE3);

0x11A70 (SCCE4)

SCC event register. This 16-bit register reports events recognized by any of the SCCs. When an event

is recognized, the SCC sets its corresponding bit in SCCE, regardless of the corresponding mask bit.

When the corresponding event occurs, an interrupt is signaled to the SIVEC register. Bits are cleared

by writing ones (writing zeros has no effect). SCCE is cleared at reset and can be read at any time.

SCCM

x

0x11A14 (SCCM1);

0x11A34 (SCCM2);

0x11A54 (SCCM3);

0x11A74 (SCCM4)

SCC mask register. The 16-bit, read/write register allows interrupts to be enabled or disabled using

the CPM for speciÞc events in each SCC channel. An interrupt is generated only if SCC interrupts in

this channel are enabled in the SIU interrupt mask register (SIMR). If an SCCM bit is zero, the CPM

does not proceed with interrupt handling when that event occurs. The SCCM and SCCE bit positions

are identical.

SCCS

x

0x11A17 (SCCS1);

0x11A37 (SCCS2);

0x11A57 (SCCS3);

0x11A77 (SCCS4)

SCC status register. This 8-bit, read-only register allows monitoring of the real-time status of RXD.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......