MOTOROLA

Chapter 22. SCC BISYNC Mode

22-17

Part IV. Communications Processor Module

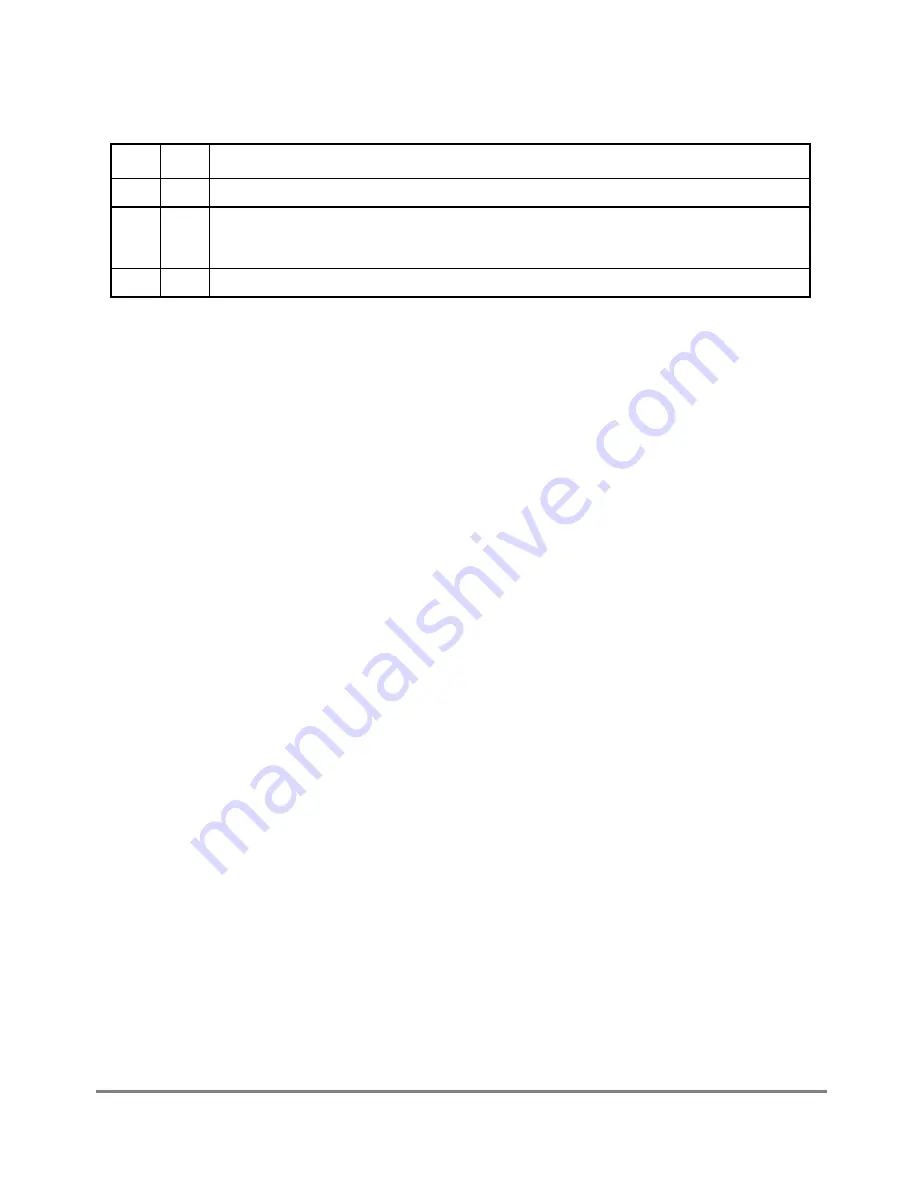

Table 22-14 describes SCCS Þelds.

22.16 Programming the SCC BISYNC Controller

Software has two ways to handle data received by the BISYNC controller. The simplest is

to allocate single-byte receive buffers, request an interrupt on reception of each buffer, and

implement BISYNC protocol entirely in software on a byte-by-byte basis. This ßexible

approach can be adapted to any BISYNC implementation. The obvious penalty is the

overhead caused by interrupts on each received character.

A more efÞcient method is to prepare and link multi-byte buffers in the RxBD table and use

software to analyze the Þrst two to three bytes of the buffer to determine the type of block

received. When this is determined, reception continues without further software

intervention until it encounters a control character, which signiÞes the end of the block and

causes software to revert to byte-by-byte reception.

To accomplish this, set SCCM[RCH] to enable an interrupt on every received byte so

software can analyze each byte. After analyzing the initial characters of a block, either set

PSMR[RTR] or issue a

RESET

BCS

CALCULATION

command. For example, if a DLE-STX is

received, enter transparent mode. By setting the appropriate PSMR bit, the controller strips

the leading DLE from DLE-character sequences. Thus, control characters are recognized

only when they follow a DLE character. PSMR[RTR] should be cleared after a DLE-ETX

is received.

Alternatively, after an SOH is received, a

RESET

BCS

CALCULATION

should be issued to

exclude SOH from BCS accumulation and reset the BCS. Notice that PSMR[RBCS] is not

needed because the controller automatically excludes SYNCs and leading DLEs.

After the type of block is recognized, SCCE[RCH] should be masked. The core does not

interrupt data reception until the end of the current block, which is indicated by the

reception of a control character matching the one in the receive control character table.

Using Table 22-15, the control character table should be set to recognize the end of the

block.

Table 22-14. SCCS Field Descriptions

Bit

Name

Description

0Ð5

Ñ

Reserved, should be cleared.

6

CS

Carrier sense (DPLL). Shows the real-time carrier sense of the line as determined by the DPLL.

0 The DPLL does not sense a carrier.

1 The DPLL senses a carrier.

7

Ñ

Reserved, should be cleared.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......