MOTOROLA

Chapter 23. SCC Transparent Mode

23-3

Part IV. Communications Processor Module

After a buffer is full, the SCC clears RxBD[E] and generates a maskable interrupt if

RxBD[I] is set. It moves to the next RxBD in the table and begins moving data to its buffer.

If the next buffer is not available, SCCE[BSY] signiÞes a busy signal that can generate a

maskable interrupt. The receiver reverts to hunt mode when an

ENTER

HUNT

MODE

command or an error is received. If GSMR_H[REVD] is set, the bit order of each byte is

reversed before it is written to memory.

Setting GSMR_H[RFW] reduces receiver latency by making the receive FIFO smaller,

which may cause receiver overruns at higher transmission speeds. The receiver always

checks the CRC of the received frame, according to GSMR_H[TCRC]. If a CRC is not

required, resulting errors can be ignored.

23.4 Achieving Synchronization in Transparent Mode

Once the SCC transmitter is enabled for transparent operation, the TxBD is prepared and

the transmit FIFO is preloaded by the SDMA channel, another process must occur before

data can be sent. It is called transmit synchronization. Similarly, once the SCC receiver is

enabled for transparent operation in the GSMR and the RxBD is made empty for the SCC,

receive synchronization must occur before data can be received. An in-line synchronization

pattern or an external synchronization signal can provide bit-level control of the

synchronization process when sending or receiving.

23.4.1 Synchronization in NMSI Mode

This section describes synchronization in NMSI mode.

23.4.1.1 In-Line Synchronization Pattern

The transparent channel can be programmed to receive a synchronization pattern. This

pattern is deÞned in the data synchronization register, DSR; see Section 19.1.3, ÒData

Synchronization Register (DSR).Ó Pattern length is speciÞed in GSMR_H[SYNL], as

shown in Table 23-1. See also Section 19.1.1, ÒThe General SCC Mode Registers

(GSMR1ÐGSMR4)

.Ó

If a 4-bit SYNC is selected, reception begins as soon as these four bits are received,

beginning with the Þrst bit following the 4-bit SYNC. The transmitter synchronizes on the

receiver pattern if GSMR_H[RSYN] = 1.

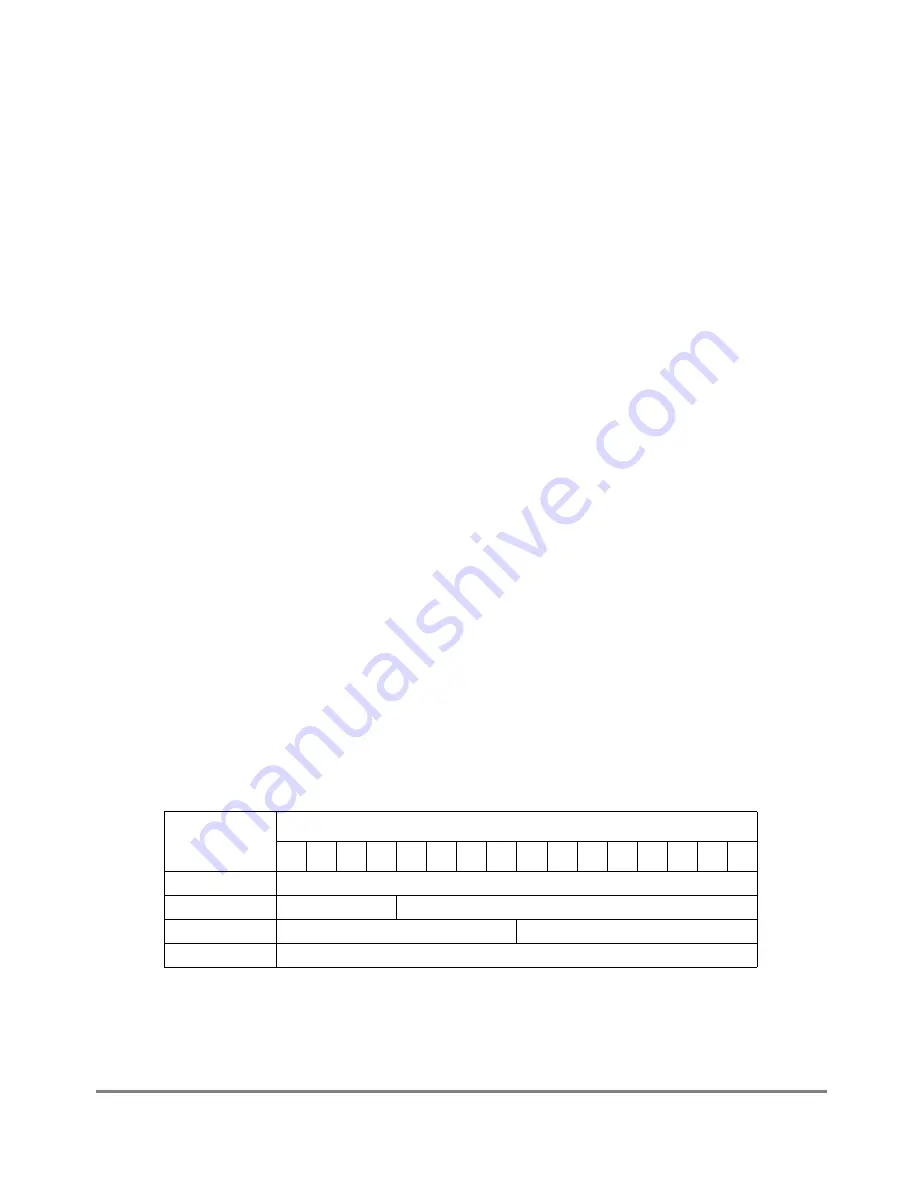

Table 23-1. Receiver SYNC Pattern Lengths of the DSR

GSMR_H[SYNL]

Setting

Bit Assignments

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

00

An external SYNC signal is used instead of the SYNC pattern in the DSR.

01

4-bit

10

8-bit

11

16-bit

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......