MOTOROLA

Chapter 27. Multi-Channel Controllers (MCCs)

27-5

Part IV. Communications Processor Module

27.4 Channel Extra Parameters

Table 27-2 describes extra parameters. This table is indexed by logical channel number.

27.5 Super-Channel Table

The super channel t able entry redirects an MCC slot to a different channel number. For this

reason, the transmitter super channel uses more FIFO (2 bytesÑhalf of a single channel

transmitter FIFOÑmultiplied by the number of the channels in the super channel) in the

MCC hardware.

On the transmitter side, super channels must be deÞned in the SI RAM (see Section 14.4.3,

ÒProgramming SIx RAM Entries,Ó for details) and a super-channel table must be created.

On the receiver side, the transparent super channels that require slot synchronization must

be programmed in the SI RAM as super channels (the slot synchronization ensures that the

data is aligned in the receiver buffer starting from the Þrst time slot after a sync pulse). In

this case, 1 byte of FIFO is allocated for each super channel. Transparent super channels

that do not require slot synchronization and HDLC super channels can be programmed in

the SI RAM as regular channels pointing to the same MCC channel. In this case the FIFO

allocated for each super channel is 2 bytes (and the CP load will be lower).

The example in Figure 27-3 shows the SI RAM programming and the super-channel table

for two transmitter super channels, one including slots 1, 6, and 7 and the second 2, 3, and

4. Figure 27-4 shows the SI RAM programming for the same transparent receiver super

Table 27-2. Channel Extra Parameters

Offset

1

1

The offset relative to dual-port RAM base a XT 8*CH_NUM

Name

Width

Description

0x00

TBASE

Hword TxBD base address. Offset of the channelÕs TxBD table relative to the MCCBASE (The

base address of the BD table for this channel 8*TBASE)

0x02

TBPTR

Hword TxBD pointer. Offset of the current BD relative to the MCCBASE. TBPTR is user-initialized

to TBASE before enabling the channel or after a fatal error before reinitializing the

channel. (The address of the BD in use for this channel 8*TBPTR)

0x04

RBASE

Hword RxBD base address. Offset of the channelÕs RxBD table relative to the MCCBASE. (The

base address of the BD table for this channel 8*RBASE)

0x06

RBPTR

Hword RxBD pointer. Offset of the current BD relative to the MCCBASE. RBPTR is user-

initialized to RBASE before enabling the channel or after a fatal error before reinitializing

the channel. (The address of the BD in use for this channel 8*RTBPTR)

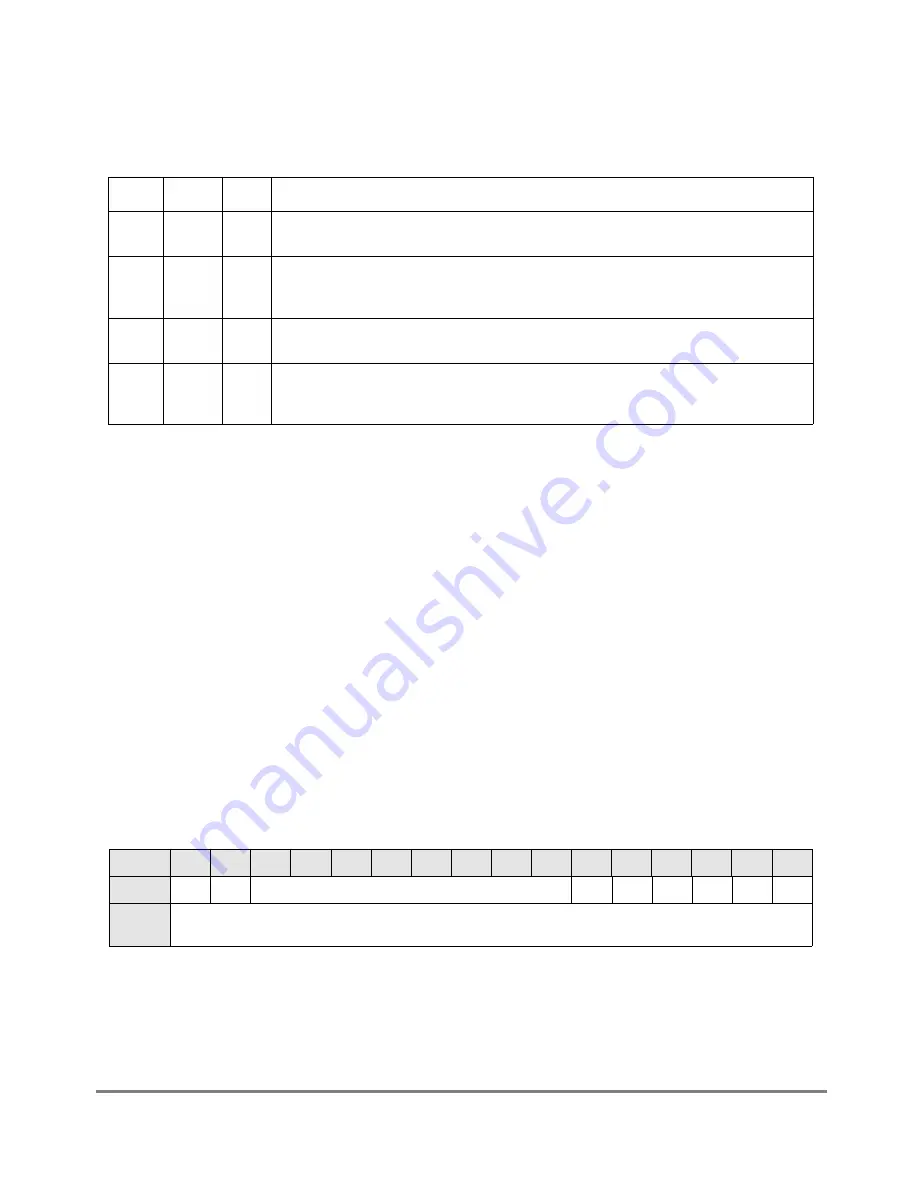

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

0

0

Channel Number

0

0

0

0

0

0

Address

DPR_base_SCTPBASE

+2*Virtual_Channel_Number

(Virtual_channel_number is the number written in the MCSEL Þeld of the corresponding SI RAM entry)

Figure 27-2. Super Channel Table Entry

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......