29-16

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

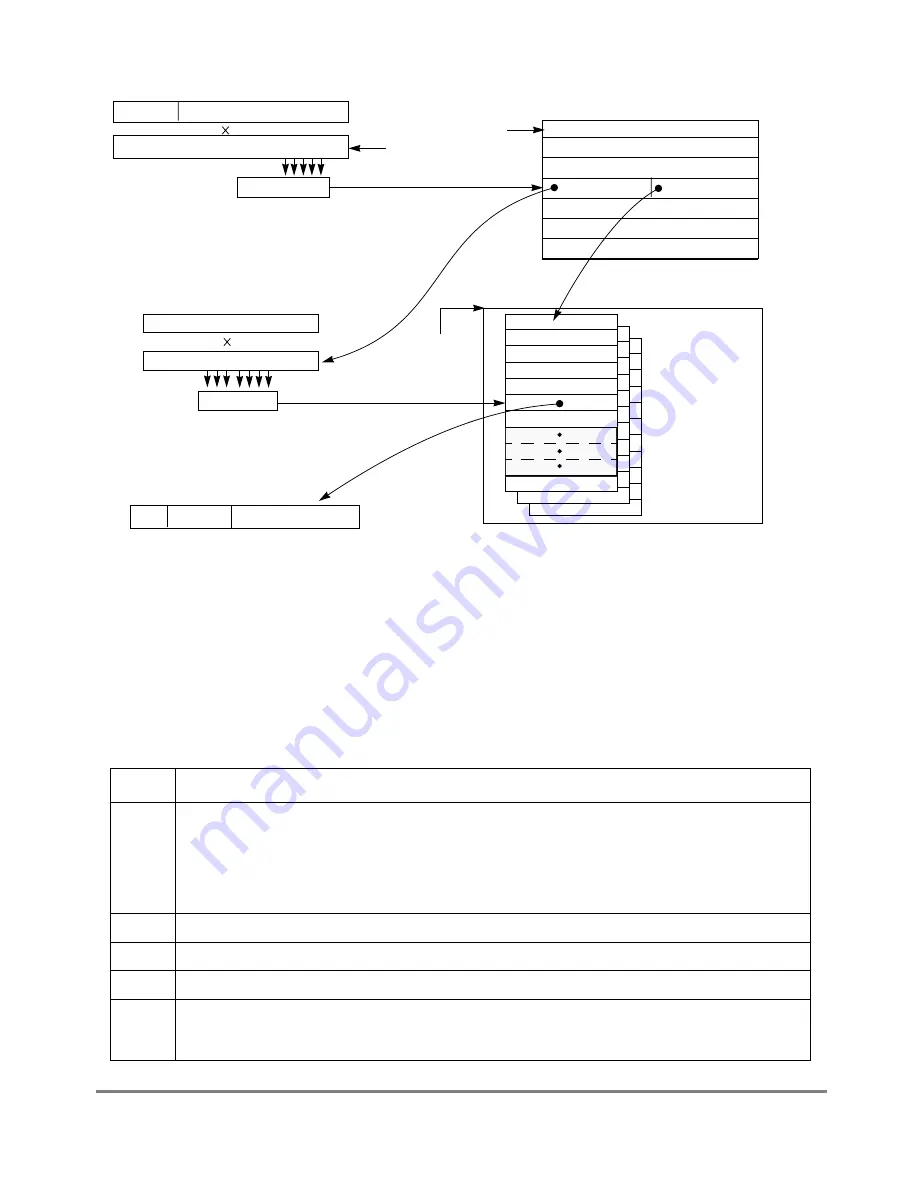

Figure 29-5. Address Compression Mechanism

Figure 29-5 shows VP_MASK selecting Þve VPI bits to index the VP-level table. The VP-

level table entry contains the 16-bit mask (VC_MASK) and the VC-level table offset

(VCOFFSET) for the next level of address mapping. The VC_MASK selects VCI bits 4Ð

10, which is used with VCT_BASE and VCOFFSET to indicate the received cellÕs channel

code.

Table 29-3. Field Descriptions for Address Compression

Field Description

PHY

Addr

In multiple PHY mode, this Þeld contains the 4 least-signiÞcant bits of the current channelÕs physical

address. Because this comparison Þeld is limited to 4 bits, two sets of look-up tables are needed if using

more than 16 PHYs.The msb of the PHY address lines (bit 4) selects between the two sets of tables. If the

msb is zero, the CP accesses the tables at VPT_BASE and VCT_BASE; if the msb is set, the CP uses

VPT1_BASE and VCT1_BASE. See Section 15.4.1, ÒCMX UTOPIA Address Register (CMXUAR).Ó

In single PHY mode, clear this Þeld.

VCI, VPI

The VCI and VPI of the current channel.

Ch Code Pointer to internal or external connection table.

Ñ

Reserved, should be cleared.

MS

Match status.

0 Match was found.

1 Match was not found.

32-bit entries

VP-level addressing table

VPI

0000

00011111

VPpointer

VPT_BASE

VCOFFSET

VC_MASK

VCI

00000111 11110000

VCpointer

32-bit entries

VC-level addressing tables

VCT_BASE

VP_MASK

16 bit

16 bit

PHY Addr

0000

16 bit

12 bit

4 bit

(in external memory)

(in dual-port RAM recommended)

Ch Code[15Ð0]

Ñ

16 bit

15 bit

MS

1 bit

31

0

31

0

0b00011

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......