29-52

MPC8260 PowerQUICC II UserÕs Manual

MOTOROLA

Part IV. Communications Processor Module

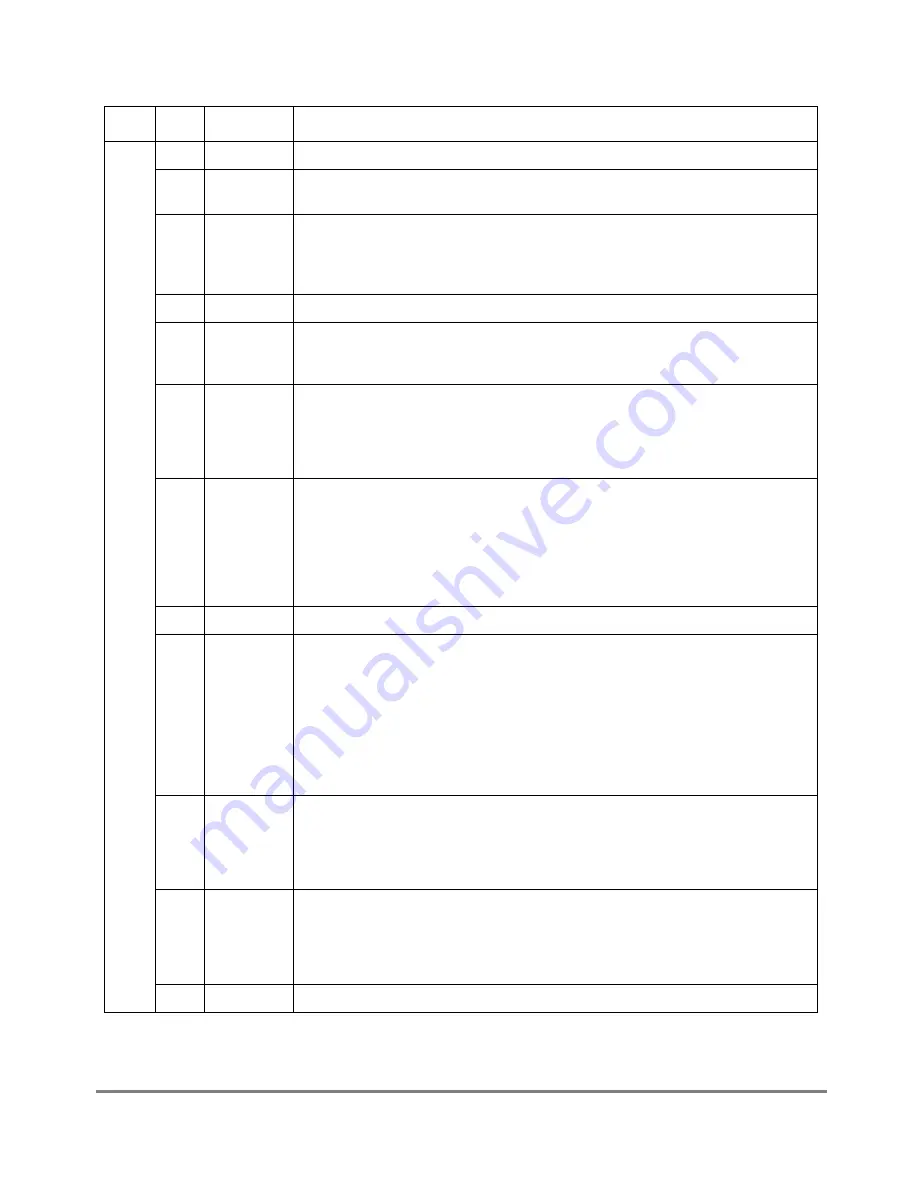

Table 29-21. TCT Field Descriptions

Offset

Bits

Name Description

0x00

0Ð1

Ñ

Reserved, should be cleared.

2

GBL

Global. Asserting GBL enables snooping of data buffers, BDs, interrupt queues and

free buffer pool.

3Ð4

BO

Byte ordering. This Þeld is used for data buffers.

00 Reserved

01 Power PC little endian

1x Big endian

5

Ñ

Reserved, should be cleared.

6

DTB

Data buffer bus

0 Reside on the 60x bus.

1 Reside on the local bus.

7

BIB

BD, interrupt queue and external SRTS logic bus

0 Reside on the 60xbus.

1 Reside on the local bus.

Note: When using AAL5, AAL1 in UDC mode, BDs and data should be placed on the

same bus (TCT[DTB]=TCT[BIB]).

8

AVCF

Auto VC off. Determines APC behavior when the last buffer associated with this VC

has been sent and no more buffers are in the VCÕs TxBD table,

0 The APC does not remove this VC from the schedule table and continues to

schedule it to transmit.

1 The APC removes this VC from the schedule table. To continue transmission after

the host adds buffers for transmission, a new

ATM

TRANSMIT

command is needed,

which can be issued only after the CP clears the VCON bit. (Bit 13)

9

Ñ

Reserved, should be cleared.

10Ð11

ATT

ATM trafÞc type

00 Peak cell-rate pacing. The host must initialize PCR and the PCR fraction. Other

trafÞc parameters are not used.

01 Peak and sustain cell rate pacing (VBR trafÞc). The APC performs a continuous-

state leaky bucket algorithm (GCRA) to pace the channel-sustain cell rate. The host

must initialize PCR, PCR fraction, SCR, SCR fraction, and BT (burst tolerance).

10 Peak and minimum cell rate pacing (UBR+ trafÞc). The host must initialize PCR,

PCR fraction, MCR, MCR fraction, and MDA.

11 Reserved

12

CPUU

CPCS-UU+CPI insertion (used for AAL5 only).

0 CPCS-UU+CPI insertion disabled. The transmitter clears the CPCS-UU+CPI Þelds.

1 CPCS-UU+CPI insertion enabled. The transmitter reads the CPCS-UU+CPI (16-bit

entry) from external memory. It should be placed after the end of the last buffer (it

should not be included in the buffer length).

13

VCON

Virtual channel is on

Should be set by the host before it issues an

ATM

TRANSMIT

command. When the host

sets TCT[STPS] (stop transmit), the CP deactivates this channel and clears VCON

when the channel is next encountered in the APC scheduling table. The host can issue

another

ATM

TRANSMIT

command only after the CP clears VCON.

14Ð15

INTQ

Points to one of four interrupt queues available.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......