MOTOROLA

Chapter 31. FCC HDLC Controller

31-13

Part IV. Communications Processor Module

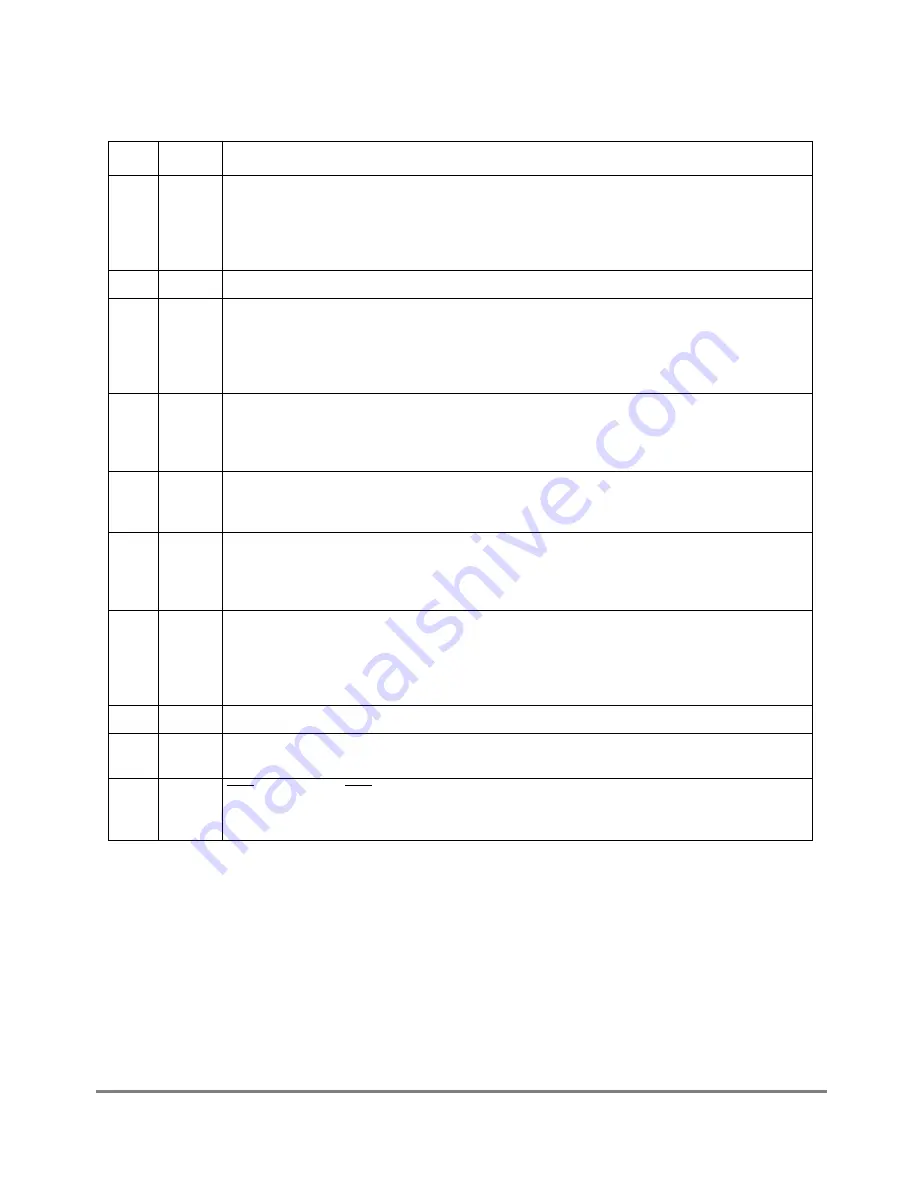

Table 31-8 describes HDLC TxBD Þelds.

The TxBD status bits are written by the HDLC controller after sending the associated data

buffer.

Table 31-8. HDLC TxBD Field Descriptions

Bits

Name

Description

0

R

Ready

0 The buffer associated with this BD is not ready for transmission. The user can manipulate this

BD or its associated buffer. The CP clears R after the buffer has been sent or an error occurs.

1 The buffer is ready to be sent. The transmission may have begun, but it has not completed. The

user cannot set Þelds in this BD once R is set.

1

Ñ

Reserved, should be cleared.

2

W

Wrap (Þnal BD in table)

0 Not the last BD in the TxBD table.

1 Last BD in the TxBD table. After this buffer has been used, the CP sends data from the Þrst BD

that TBASE points to in the table. The number of TxBDs in this table is determined only by the

W bit and the overall space constraints of the dual-port RAM.

3

I

Interrupt

0 No interrupt is generated after this buffer is serviced.

1 Either FCCE[TXB] or FCCE[TXE] is set when this buffer is serviced by the HDLC controller.

These bits can cause interrupts if they are enabled.

4

L

Last

0 Not the last buffer in the frame.

1 Last buffer in the current frame.

5

TC

Tx CRC.Valid only when the L bit is set. Otherwise, it is ignored.

0 Transmit the closing ßag after the last data byte. This setting can be used to send a bad CRC

after the data for testing purposes.

1 Transmit the CRC sequence after the last data byte.

6

CM

Continuous mode

0 Normal operation.

1 The R bit is not cleared by the CP after this BD is closed, allowing the buffer to be retransmitted

automatically the next time the CP accesses this BD. However, the R bit is cleared if an error

occurs during transmission, regardless of the CM bit.

7Ð13

Ñ

Reserved, should be cleared.

14

UN

Underrun. The HDLC controller encounters a transmitter underrun condition while sending the

buffer. The HDLC controller writes UN after sending the buffer.

15

CT

CTS lost. Set when CTS is lost during frame transmission in NMSI mode. If data from more than

one buffer is in the FIFO buffer when this error occurs, CT is set in the currently open TxBD. The

HDLC controller writes CT after sending the buffer.

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......