MOTOROLA

Chapter 34. I2C Controller

34-3

Part IV. Communications Processor Module

When the I

2

C controller is master, the SCL clock output, taken directly from the I

2

C BRG,

shifts receive data in and transmit data out through SDA. The transmitter arbitrates for the

bus during transmission and aborts if it loses arbitration. When the I

2

C controller is a slave,

the SCL clock input shifts data in and out through SDA. The SCL frequency can range from

DC to BRGCLK/48.

34.3 I

2

C Controller Transfers

To initiate a transfer, the master I

2

C controller sends a message specifying a read or write

request to an I

2

C slave. The Þrst byte of the message consists of a 7-bit slave port address

and a R/W request bit. Note that because the R/W request follows the slave port address in

the I

2

C bus speciÞcation, the R/W request bit must be placed in the lsb (bit 7) unless

operating in reverse data mode; see Section 34.4.1, ÒI2C Mode Register (I2MOD).Ó

To write to a slave, the master sends a write request (R/W = 0) along with either the target

slaveÕs address or a general call (broadcast) address of all zeros, followed by the data to be

written. To read from a slave, the master sends a read request (R/W = 1) and the target

slaveÕs address. When the target slave acknowledges the read request, the transfer direction

is reversed, and the master receives the slaveÕs transmit buffer(s). If the receiver (master or

slave) does not acknowledge each byte transfer in the ninth bit frame, the transmitter signals

a transmission error event (I2ER[TXE]). An I

2

C transfer timing diagram is shown in

Figure 34-3.

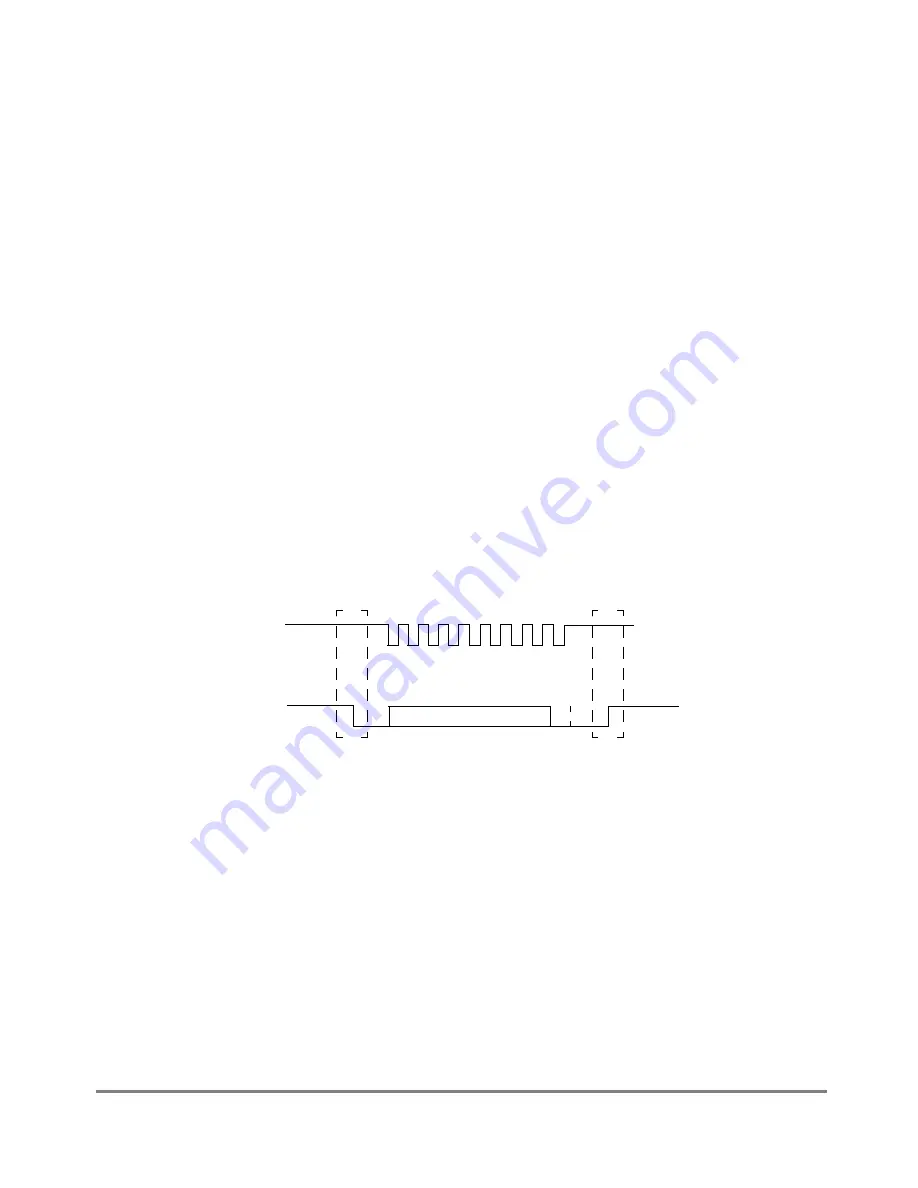

Figure 34-3. I

2

C Transfer Timing

Select master or slave mode for the controller using the I

2

C command register (I2COM[M/

S]). Set the masterÕs start bit, I2COM[STR], to begin a transfer; setting a slaveÕs

I2COM[STR] activates the slave to wait for a transfer request from a master.

If a master or slave transmitterÕs current TxBD[L] is set, transmission stops once the buffer

is sent; that is, I2COM[STR] must be set again to reactivate transfers. If TxBD[L] is zero,

once the current buffer is sent, the controller begins processing the next TxBD without

waiting for I2COM[STR] to be set again.

The following sections further detail the transfer process.

SCL

SDA

Data Byte

Start Condition

Stop Condition

A

C

K

7

8

9

4

5

6

1

2

3

Summary of Contents for MPC8260 PowerQUICC II

Page 1: ...MPC8260UM D 4 1999 Rev 0 MPC8260 PowerQUICC II UserÕs Manual ª ª ...

Page 66: ...lxvi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA ...

Page 88: ...1 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 120: ...2 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part I Overview ...

Page 138: ...Part II iv MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II Configuration and Reset ...

Page 184: ...4 46 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part II ConÞguration and Reset ...

Page 202: ...Part III vi MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 266: ...8 34 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 382: ...10 106 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 392: ...11 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part III The Hardware Interface ...

Page 430: ...Part IV viii MOTOROLA Part IV Communications Processor Module ...

Page 490: ...14 36 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 524: ...17 10 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 556: ...18 32 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 584: ...19 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 632: ...21 24 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 652: ...22 20 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 668: ...23 16 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 758: ...27 28 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 780: ...28 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 874: ...29 94 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 920: ...31 18 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Part IV Communications Processor Module ...

Page 980: ...A 4 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA Appendixes ...

Page 1002: ...Index 22 MPC8260 PowerQUICC II UserÕs Manual MOTOROLA INDEX ...

Page 1006: ......