MVME1600-001 Base Board Preparation

1-8

1

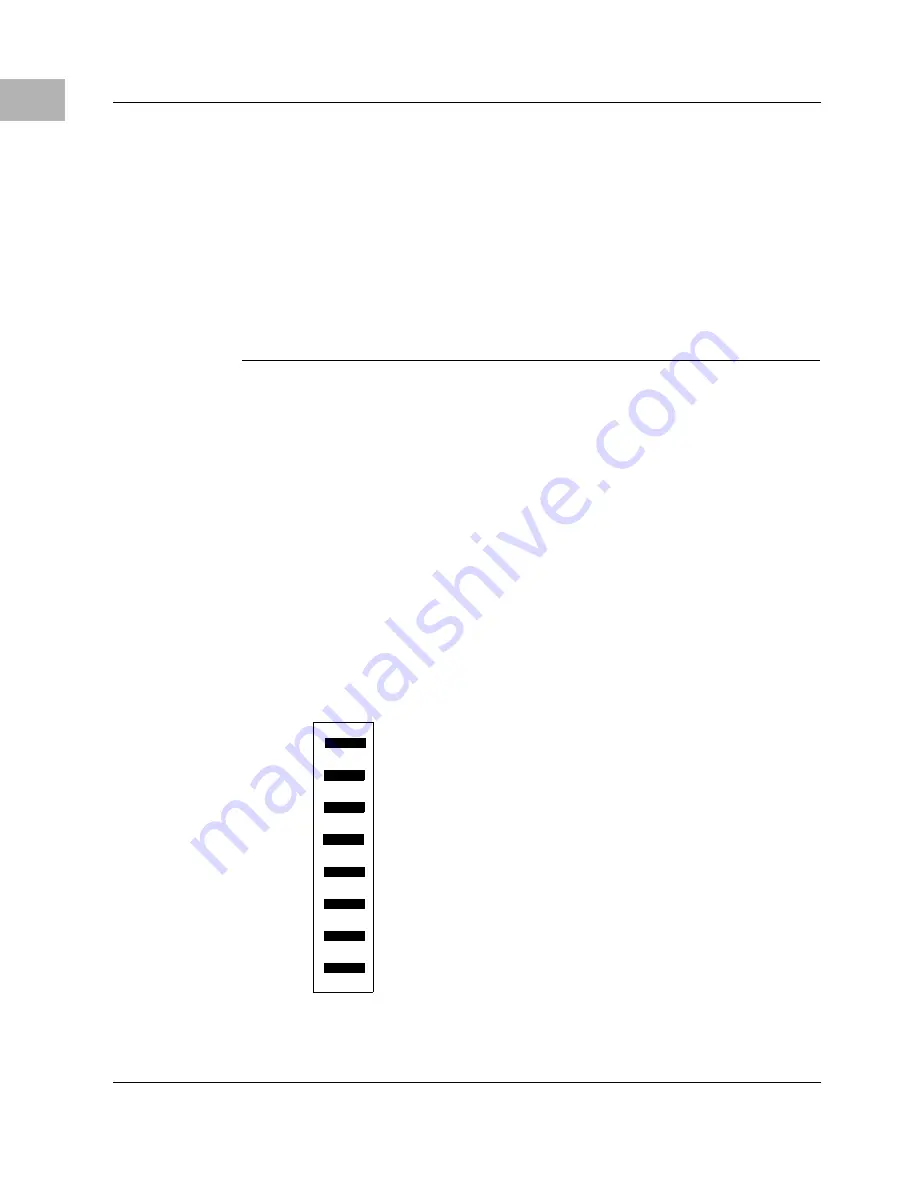

General-Purpose Software-Readable Header (J8)

Header J8 provides eight readable jumpers. These jumpers can be read as

a register at ISA I/O address $80000801. Bit 0 is associated with header

pins 1 and 2; bit 7 is associated with pins 15 and 16. The bit values are read

as a zero when the jumper is installed, and as a one when the jumper is

removed. The PowerPC firmware (PPCBug) reserves the four lower-order

bits, SRH3 to SRH0. They are defined as shown in the list below:

The four higher-order bits, SRH4 to SRH7, are user-definable. They can

be allocated as necessary to specific applications. The MVME1600-001 is

shipped from the factory with J8 set to all zeros (jumpers on all pins).

Low-Order Bit

Pins

Definition

Bit #0 (SRH0)

1—2

Reserved for future use.

Bit #1 (SRH1)

3—4

With the jumper installed between pins 3 and 4

(factory configuration), the debugger uses the

current user setup/operation parameters in

NVRAM. When the jumper is removed (making

the bit a 1), the debugger uses the default

setup/operation parameters in ROM instead. Refer

to the ENV command description in Chapter 6 for

the ROM defaults.

Bit #2 (SRH2)

5—6

Reserved for future use.

Bit #3 (SRH3)

7—8

Reserved for future use.

J8

2

SRH7

SRH6

SRH5

SRH1

SRH4

SRH3

SRH2

16

15

1

SRH0

USER-DEFINABLE

USER-DEFINABLE

USER-DEFINABLE

SETUP PARAMETER SOURCE (IN=NVRAM; OUT=ROM)

USER-DEFINABLE

RESERVED FOR FUTURE USE

RESERVED FOR FUTURE USE

RESERVED FOR FUTURE USE

PPCBug INSTALLED

8

7

Summary of Contents for MVME1603

Page 1: ...MVME1603 MVME1604 Single Board Computer Installation and Use V1600 1A IH4 ...

Page 14: ...xiv ...

Page 156: ...Using the Debugger 5 8 5 ...

Page 176: ...ENV Set Environment 6 20 6 ...

Page 190: ...EMC Compliance B 4 B ...

Page 200: ...Proper Grounding C 10 C ...

Page 222: ......