LCSR Programming Model

http://www.motorola.com/computer/literature

2-51

2

I2WP

When this bit is high, write posting is enabled to the local

bus F page. When this bit is low, write posting is disabled

to the local bus F page.

I2EN

When this bit is high, the F page ($F0000000 through

$FF7FFFFF) map decoder is enabled. The F0 page is

defined as A24/D16 on the VMEbus while the F1-FE

pages are defined as A32/D16. When this bit is low, the F

page is disabled.

ROM Control Register

This function is not used on the MVME1x7P.

Programming the VMEchip2 DMA Controller

This section includes programming information on the DMA controller,

VMEbus interrupter, MPU status register, and local-bus-to-VMEbus

requester register.

The VMEchip2 features a local-bus -to-VMEbus DMA controller

(DMAC). The DMAC has two modes of operation: command chaining,

and direct. In direct mode, the local bus address, the VMEbus address, the

byte count, and the control register of the DMAC are programmed and the

DMAC is enabled. The DMAC transfers data, as programmed, until the

byte count is zero or an error is detected. When the DMAC stops, the status

bits in the DMAC status register are set and an interrupt is sent to the local

bus interrupter. If the DMAC interrupt is enabled in the local bus

interrupter, the local bus is interrupted. The time on and time off timers

should be programmed to control the VMEbus bandwidth used by the

DMAC.

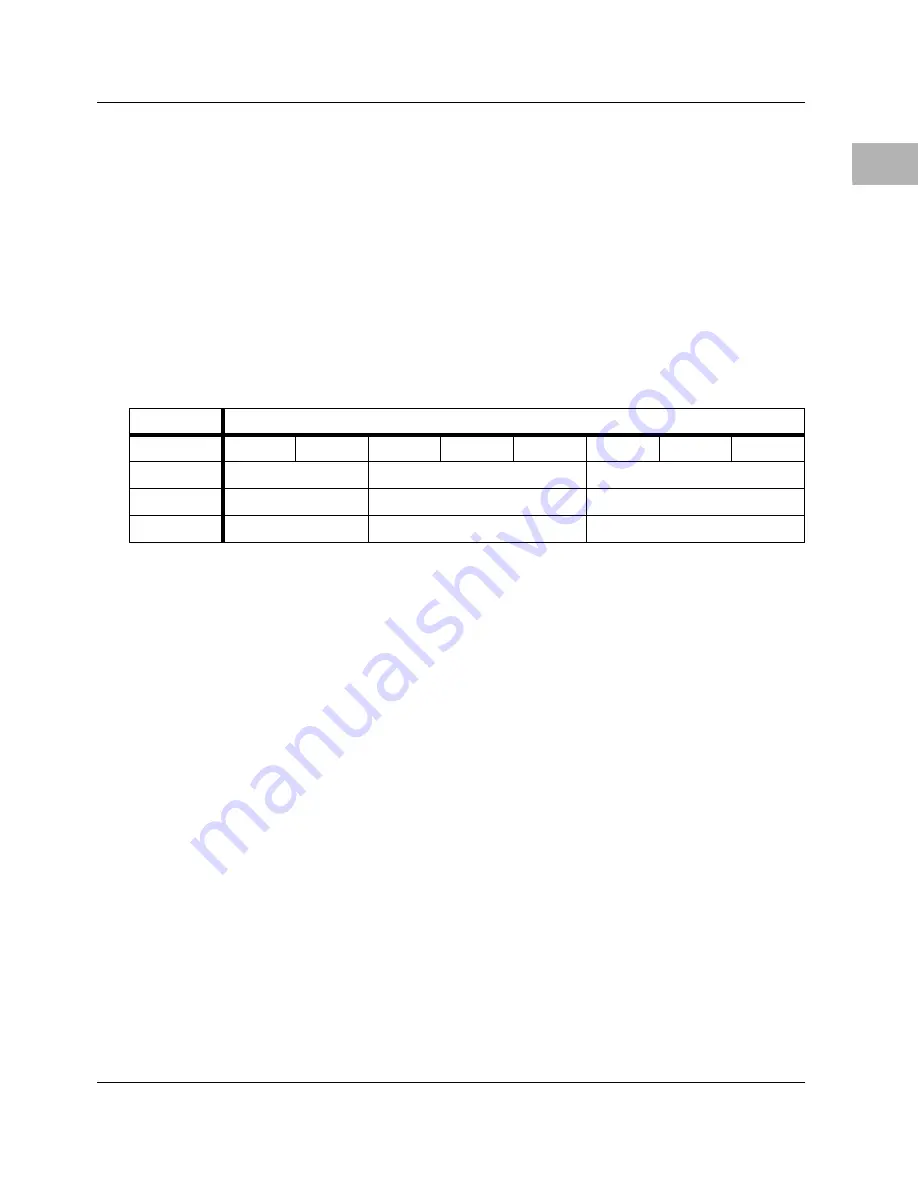

ADR/SIZ

$FFF4002C

BIT

7

6

5

4

3

2

1

0

NAME

SIZE

BSSPD

ASPD

OPER

R/W

R/W

R/W

RESET

0 PS

0 PS

0 PS

Summary of Contents for MVME1X7P

Page 16: ...xvi ...

Page 18: ...xviii ...

Page 20: ...xx ...

Page 26: ...xxvi ...

Page 90: ...1 64 Computer Group Literature Center Web Site Programming Issues 1 ...

Page 248: ...3 50 Computer Group Literature Center Web Site PCCchip2 3 ...

Page 286: ...4 38 Computer Group Literature Center Web Site MCECC Functions 4 ...

Page 288: ...A 2 Computer Group Literature Center Web Site Summary of Changes A ...

Page 316: ...Index IN 14 Computer Group Literature Center Web Site I N D E X ...