2-50

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

edge of CLK after RST_ has been released. All of the sampled pins are

cascaded with several layers of registers to eliminate problems with hold

time.

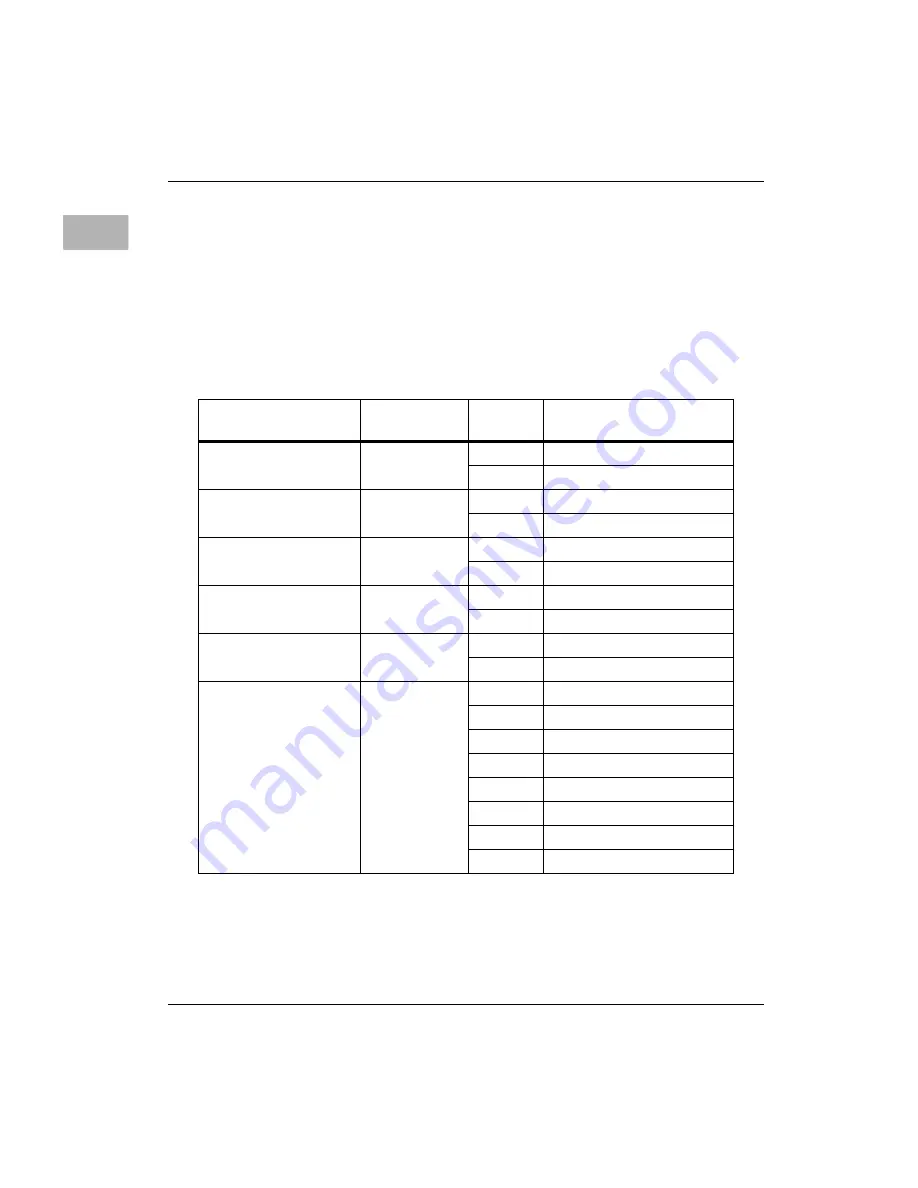

summarizes the hardware configuration options that relate to

the PHB.

Table 2-15. PHB Hardware Configuration

Function

Sample Pin(s)

Sampled

State

Meaning

PCI 64-bit Enable

REQ64_

0

64-bit PCI Bus

1

32-bit PCI Bus

PPC Register Base

RD[5]

0

Register Base = $FEFF0000

1

Register Base = $FEFE0000

MPIC Interrupt Type

RD[7]

0

Parallel Interrupts

1

Serial Interrupts

PPC Arbiter Mode

RD[8]

0

Disabled

1

Enabled

PCI Arbiter Mode

RD[9]

0

Disabled

1

Enabled

PPC:PCI Clock Ratio

RD[10:12]

000

Reserved

100

1:1

010

2:1

110

3:1

001

3:2

101

Reserved

011

5:2

111

Reserved

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...