Registers

http://www.motorola.com/computer/literature

2-77

2

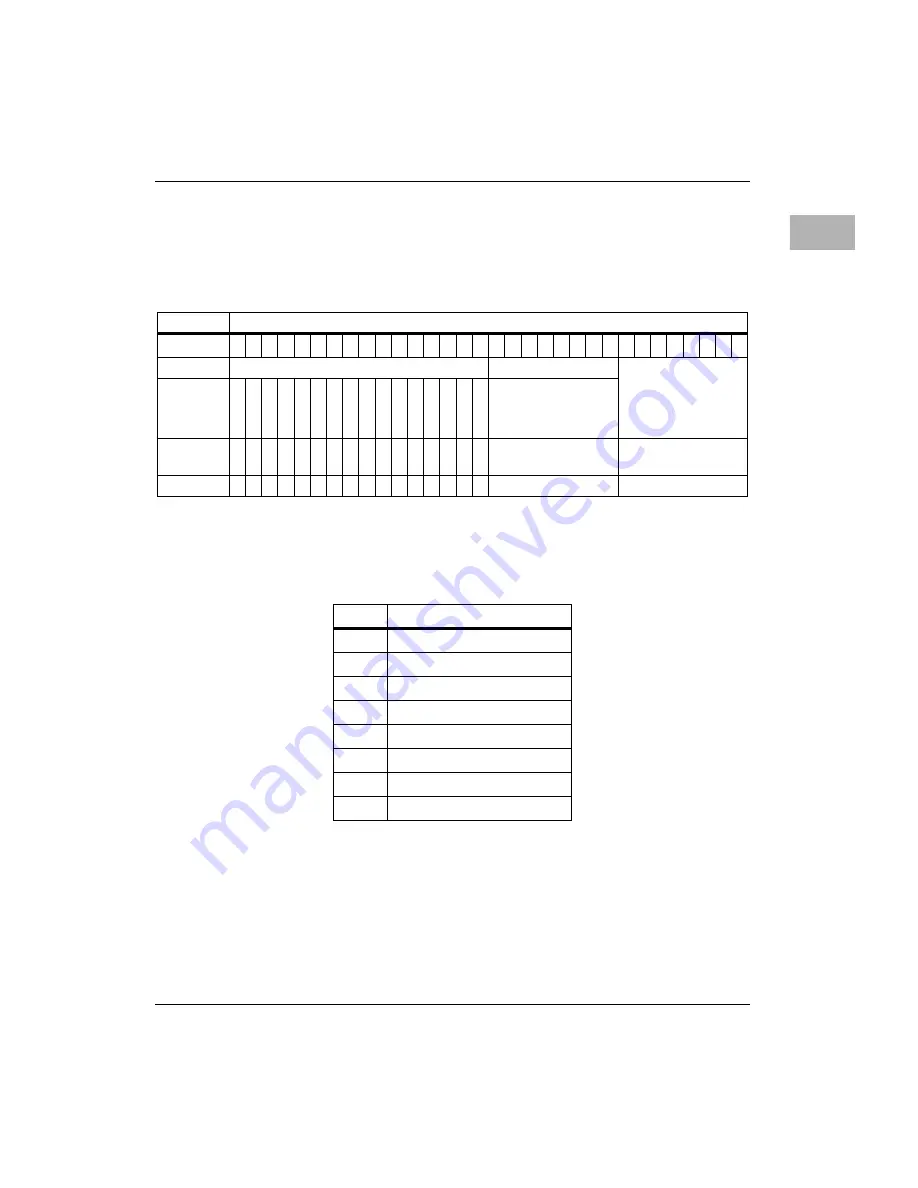

Hardware Control-Status/Prescaler Adjust Register

The Hardware Control-Status Register (HCSR) provides hardware

specific control and status information for the PHB. The bits within the

HCSR are defined as follows:

XPRx

PPC/PCI Clock Ratio. This is a read only field that is used

to indicate the clock ratio that has been established by the

PHB at the release of reset. The encoding of this field is

shown in the following table.

SPRQ

Speculative PCI Request. If set, the PHB PCI Master will

perform speculative PCI requesting when a PCI bound

transaction has been retried due to bridge lock resolution.

If cleared, the PCI Master will only request the PCI bus

when a transaction is pending within the PHB FIFOs.

Address

$FEFF0010

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

HCSR

XPAD

XP

R2

XP

R1

XP

R0

SP

RQ

WL

R

T

1

WL

R

T

0

RLR

T

1

RLR

T

0

Operation

R

R

R

R

R

R

R

R

R

R

R

R/W

R/W

R/W

R/W

R/W

R

R/W

Reset

0

0

0

0

0

X

X

X

0

0

0

1

0

0

0

0

$00

$9C

XPR

PPC60x/PCI clock ratio

000

Undefined

001

1:1

010

2:1

011

3:1

100

3:2

101

Undefined

110

5:2

111

Undefined

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...