Registers

http://www.motorola.com/computer/literature

2-79

2

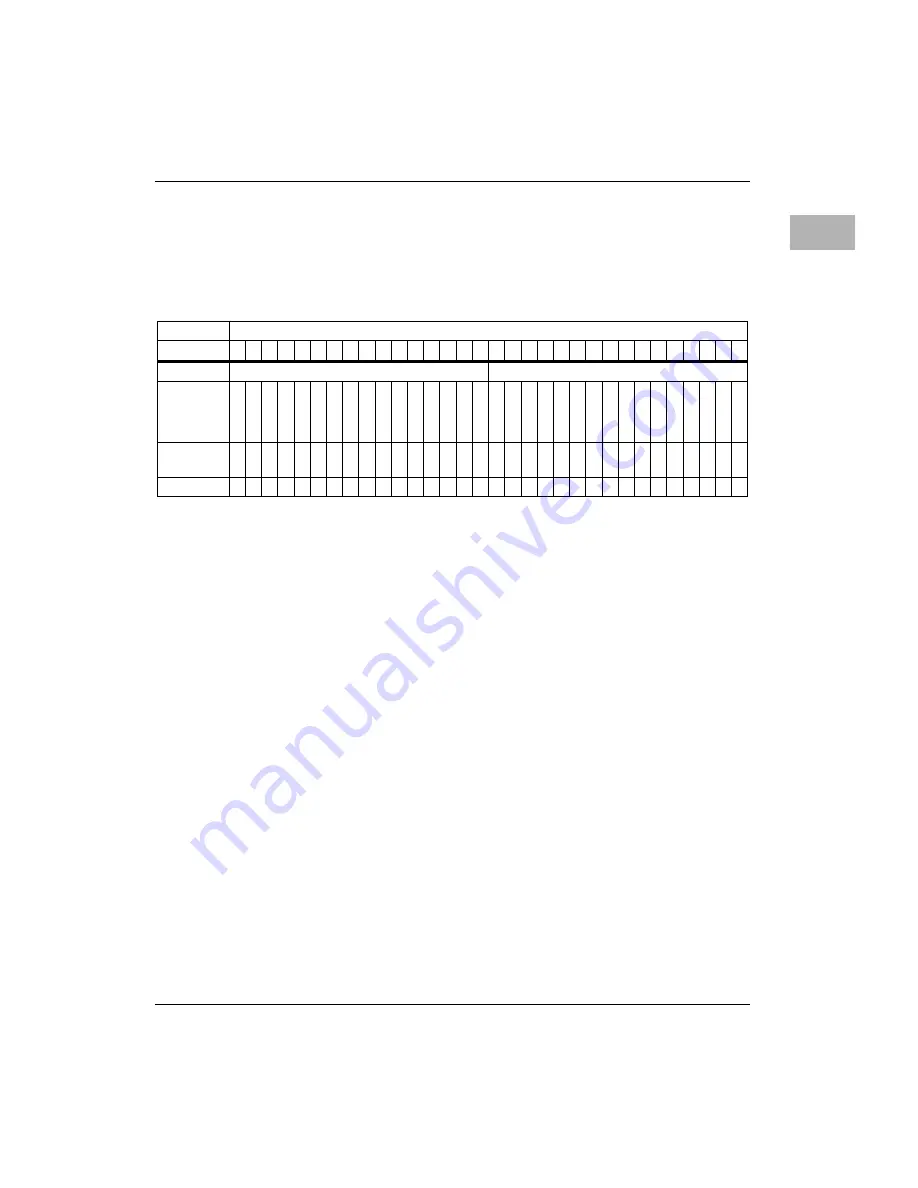

PPC Error Test/Error Enable Register

The Error Test Register (ETEST) provides you with a way to send certain

types of errors to test the PHB error capture and status circuitry. The bits

within the ETEST are defined as follows:

DPEx

Data Parity Error Enable. These bits are used for test

reasons to purposely inject data parity errors whenever the

PHB is sourcing PPC data. A data parity error will be

created on the corresponding PPC data parity bus if a bit

is set. For example, setting DPE0 will cause DP0 to be

generated incorrectly. If the bit is cleared, the PHB will

generate correct data parity.

APEx

Address Parity Error Enable. These bits are used for test

reasons to purposely inject address parity errors whenever

the PHB is acting as a PPC bus master. An address parity

error will be created on the corresponding PPC address

parity bus if a bit is set. For example, setting APE0 will

cause AP0 to be generated incorrectly. If the bit is cleared,

the PHB will generate correct address parity.

The Error Enable Register (EENAB) controls how the PHB is to respond

to the detection of various errors. In particular, each error type can

uniquely be programmed to generate a machine check, generate an

interrupt, generate both, or generate neither. The bits within the ETEST are

defined as follows:

Address

$FEFF0020

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

ETEST

EENAB

DP

E

0

DP

E

1

DP

E

2

DP

E

3

DP

E

4

DP

E

5

DP

E

6

DP

E

7

APE0

APE1

APE2

APE3

DF

L

T

XB

T

O

M

XDPEM

PP

E

R

M

PS

E

R

M

PS

MAM

PR

T

A

M

XB

T

O

II

XDP

E

I

PP

ERI

PS

ERI

PS

M

A

I

PR

T

A

I

Operation

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R

R

R/

W

R/

W

R/

W

R/

W

R

R/

W

R/

W

R/

W

R/

W

R/

W

R/

W

R/

W

R

R

R/

W

R/

W

R/

W

R/

W

R/

W

R/

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...