2-102

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

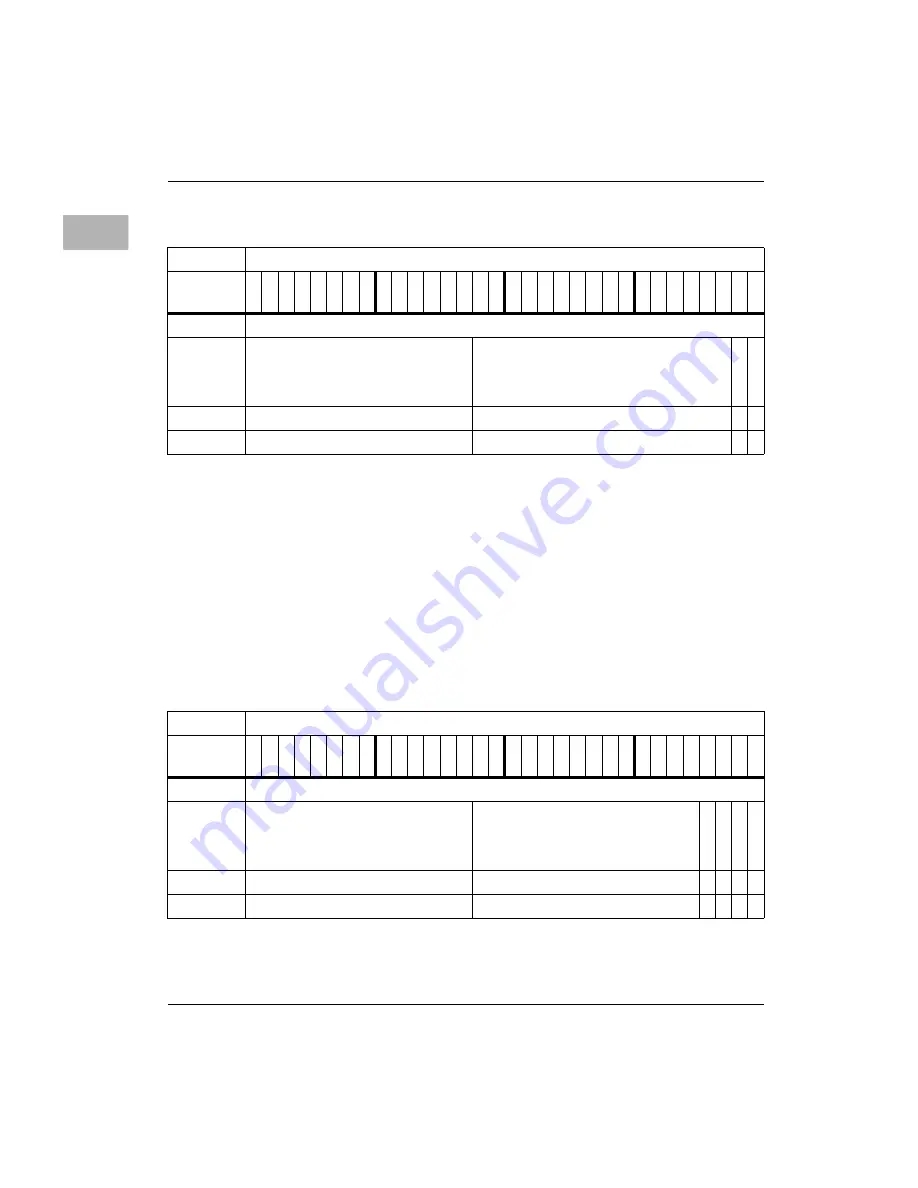

MPIC I/O Base Address Register

The MPIC I/O Base Address Register (MIBAR) controls the mapping of

the MPIC control registers in PCI I/O space.

IO/MEM

IO Space Indicator. This bit is hard-wired to a logic one to

indicate PCI I/O space.

RES

Reserved. This bit is hard-wired to zero.

BASE

Base Address. These bits define the I/O space base

address of the MPIC control registers. The MIBAR

decoder is disabled when the BASE value is zero.

MPIC Memory Base Address Register

Offset

$10

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

MIBAR

BASE

RES

IO/MEM

Operation

R/W

R

R

R

Reset

$0000

$0000

0

1

Offset

$14

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

MMBAR

BASE

PR

E

MTYP

1

MTYP

0

IO/MEM

Operation

R/W

R

R

R

R

R

Reset

$0000

$0000

0

0

0

0

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...