2-114

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

NIRQ

NUMBER OF IRQs. The number of the highest external

IRQ source supported. The IPI, Timer, and PHB Detected

Error interrupts are excluded from this count.

NCPU

NUMBER OF CPUs. The number of the highest physical

CPU supported. There are two CPUs supported by this

design. CPU #0 and CPU #1.

VID

VERSION ID. Version ID for this interrupt controller.

This value reports what level of the specification is

supported by this implementation. Version level of 02 is

used for the initial release of the MPIC specification.

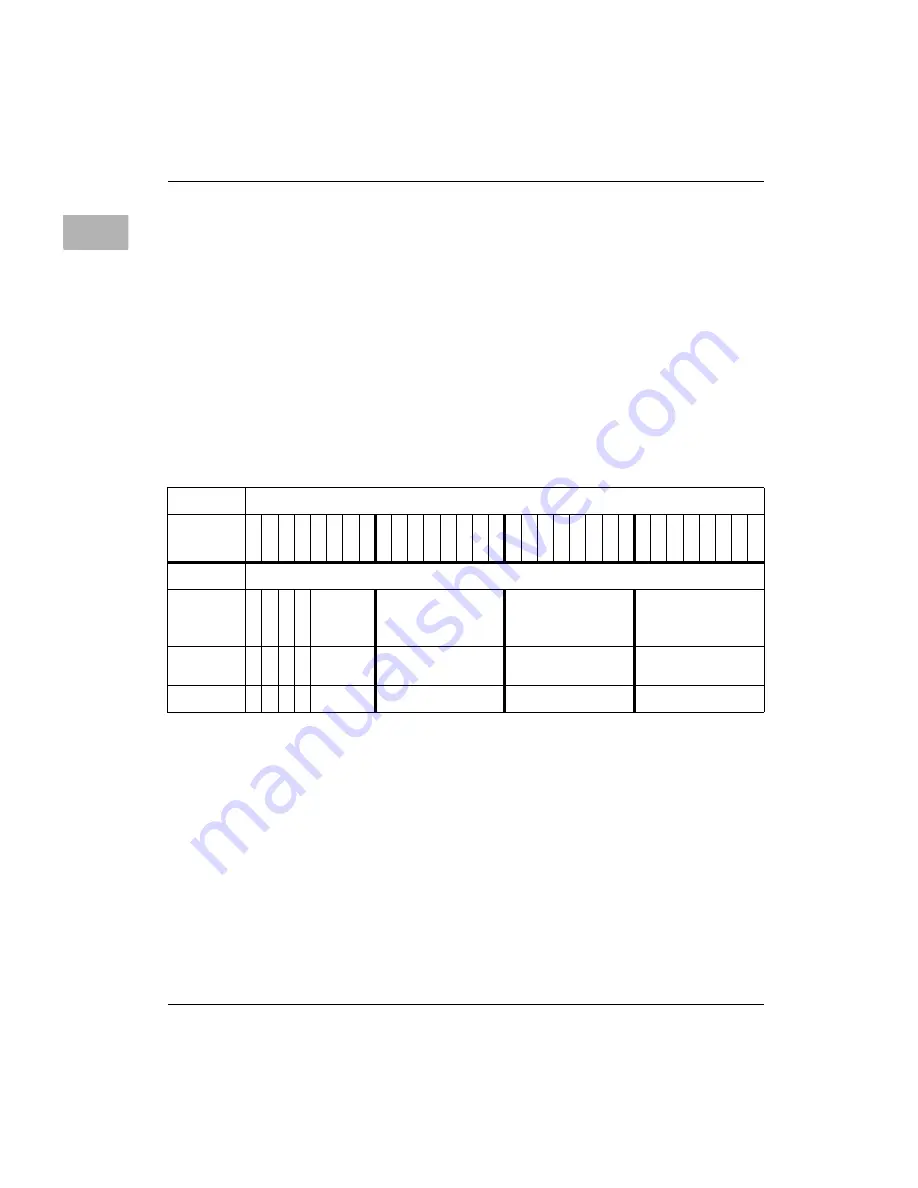

Global Configuration Register

RESET RESET

CONTROLLER. Writing a one to this bit forces

the controller logic to be reset. This bit is cleared

automatically when the reset sequence is complete. While

this bit is set, the values of all other register are undefined.

EINTT

External Interrupt Type. This read only bit indicates the

external interrupt type: serial or parallel mode. When this

bit is set MPIC is in serial mode for external interrupts 0

through 15. When this bit is cleared MPIC is in parallel

mode for external interrupts.

Offset

$01020

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

GLOBAL CONFIGURATION

RESET

EINTT

M

TIE

Operation

C

R

R/W

R/W

R

R

R

R

Reset

0

0

0

0

$00

$00

$00

$00

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...