Functional Description

http://www.motorola.com/computer/literature

3-7

3

Page Holding

Further savings comes when the new address is close enough to a previous

one that it falls within an open page in the SDRAM array. When this

happens, the SMC can transfer the data for the next cycle without having

to wait to activate a new page in SDRAM. In the SMC this feature is

referred to as page holding.

SDRAM Speeds

The SDRAM that the Hawk ASIC controls use the 60x clock. The SMC

can be configured to operate at several different 60x clock frequencies

using SDRAMs that have various speed characteristics. The bits that

control this configuration are located in the SDRAM Speed Attributes

Register, which is described in the Register portion of this section. Refer

to

for some specific timing numbers.

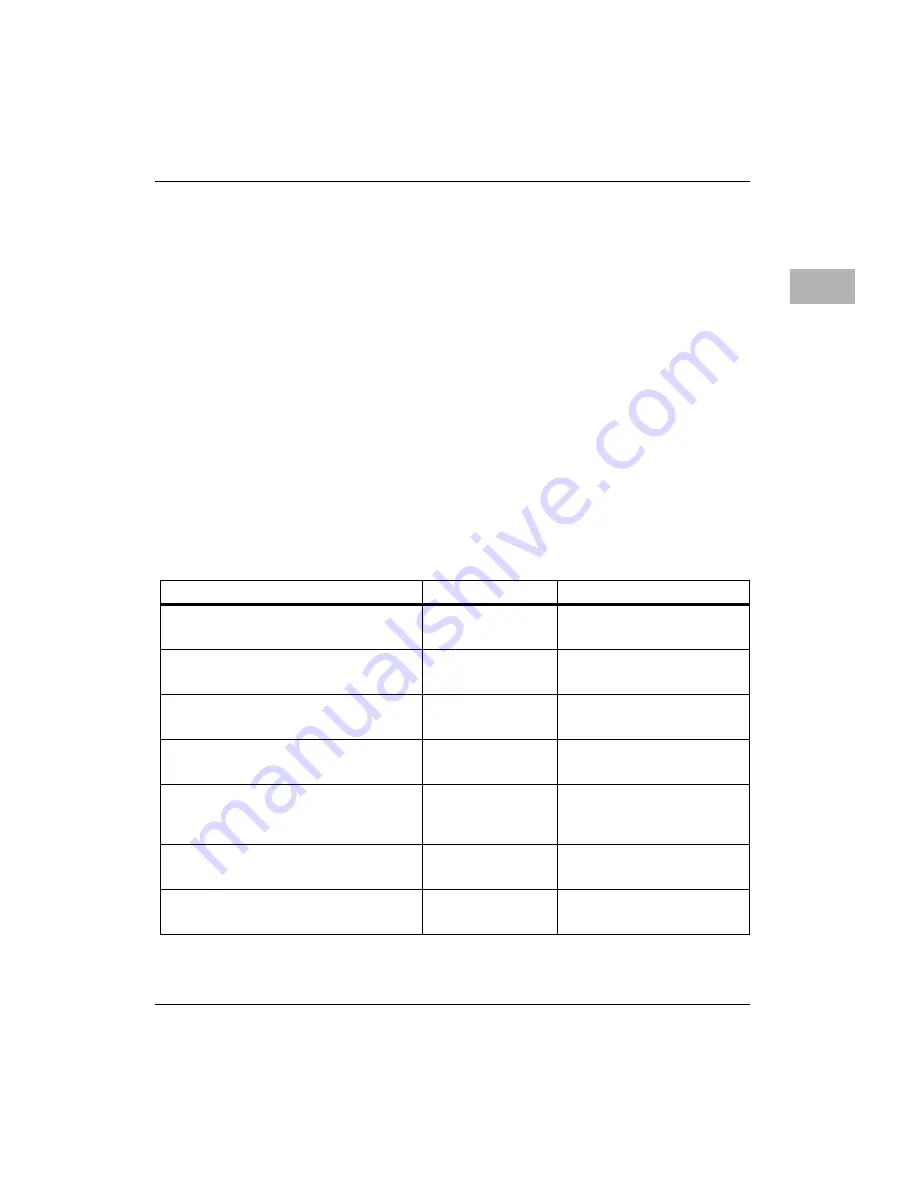

Table 3-1. 60

x

Bus to SDRAM Estimated Access Timing at 100 MHz with PC100

SDRAMs (CAS_latency of 2)

Access Type

Access Time

Comments

4-Beat Read after idle,

SDRAM Bank Inactive

10-1-1-1

4-Beat Read after idle,

SDRAM Bank Active - Page Miss

12-1-1-1

4-Beat Read after idle,

SDRAM Bank Active - Page Hit

7-1-1-1

4-Beat Read after 4-Beat Read,

SDRAM Bank Active - Page Miss

5-1-1-1

4-Beat Read after 4-Beat Read,

SDRAM Bank Active - Page Hit

2.5-1-1-1

2.5-1-1-1 is an average of 2-

1-1-1 half of the time and 3-

1-1-1 the other half.

4-Beat Write after idle,

SDRAM Bank Active or Inactive

4-1-1-1

4-Beat Write after 4-Beat Write,

SDRAM Bank Active - Page Miss

6-1-1-1

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...