3-8

Computer Group Literature Center Web Site

System Memory Controller (SMC)

3

Notes

1. SDRAM speed attributes are programmed for the

following: CAS_latency = 2, tRCD = 2 CLK Periods, tRP =

2CLK Periods, tRAS = 5 CLK Periods, tRC = 7 CLK

Periods, tDP = 2 CLK Periods, and the swr dpl bit is set in

the SDRAM Speed Attributes Register.

2. The Hawk is configured for “no external registers” on the

SDRAM control signals.

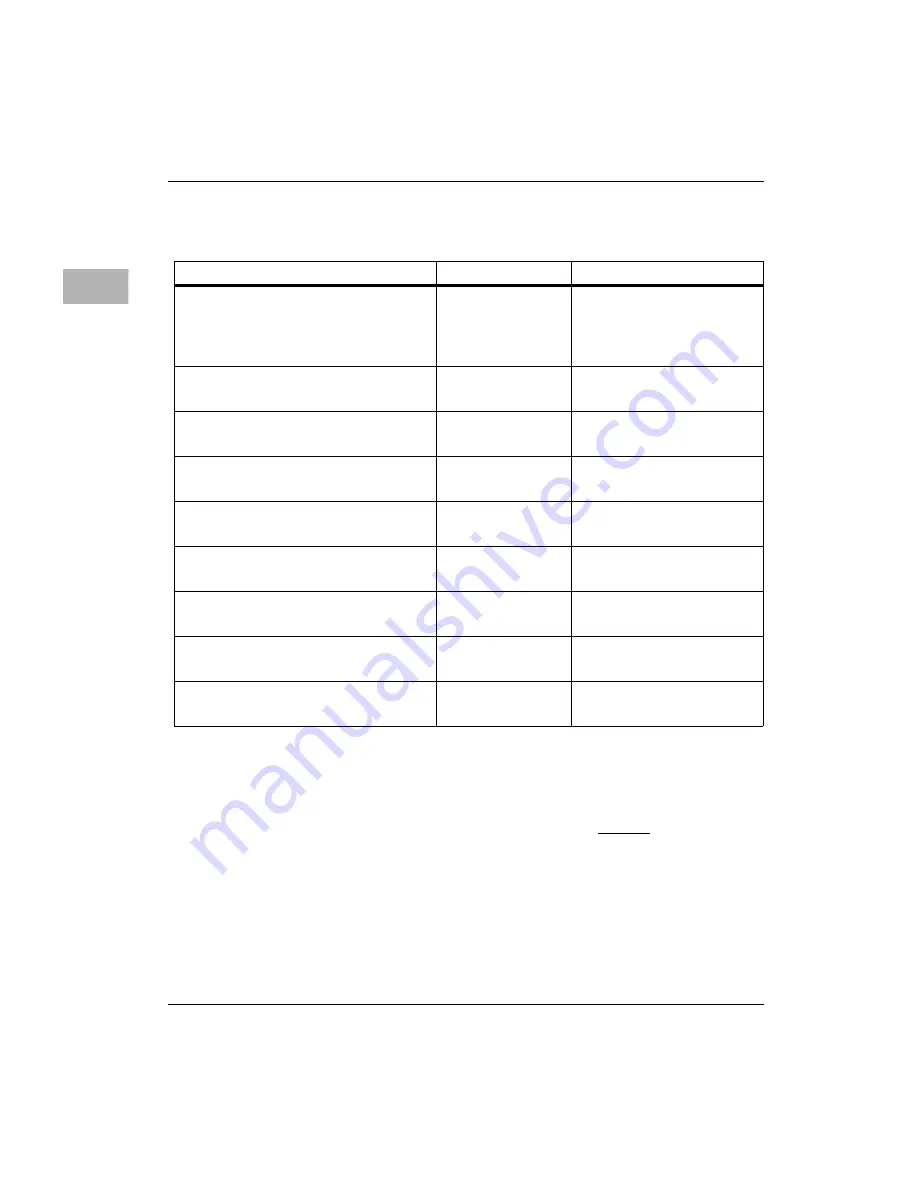

4-Beat Write after 4-Beat Write,

SDRAM Bank Active - Page Hit

3-1-1-1

3-1-1-1 for the second burst

write after idle.

2-1-1-1 for subsequent burst

writes.

1-Beat Read after idle,

SDRAM Bank Inactive

10

1-Beat Read after idle,

SDRAM Bank Active - Page Miss

12

1-Beat Read after idle,

SDRAM Bank Active - Page Hit

7

1-Beat Read after 1-Beat Read,

SDRAM Bank Active - Page Miss

8

1-Beat Read after 1-Beat Read,

SDRAM Bank Active - Page Hit

5

1-Beat Write after idle,

SDRAM Bank Active or Inactive

5

1-Beat Write after 1-Beat Write,

SDRAM Bank Active - Page Miss

13

1-Beat Write after 1-Beat Write,

SDRAM Bank Active - Page Hit

8

Table 3-1. 60

x

Bus to SDRAM Estimated Access Timing at 100 MHz with PC100

SDRAMs (CAS_latency of 2) (Continued)

Access Type

Access Time

Comments

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...