3-20

Computer Group Literature Center Web Site

System Memory Controller (SMC)

3

Notes

The information in

applies to access timing when

configured for devices with an access time equal to 8 clock

periods.

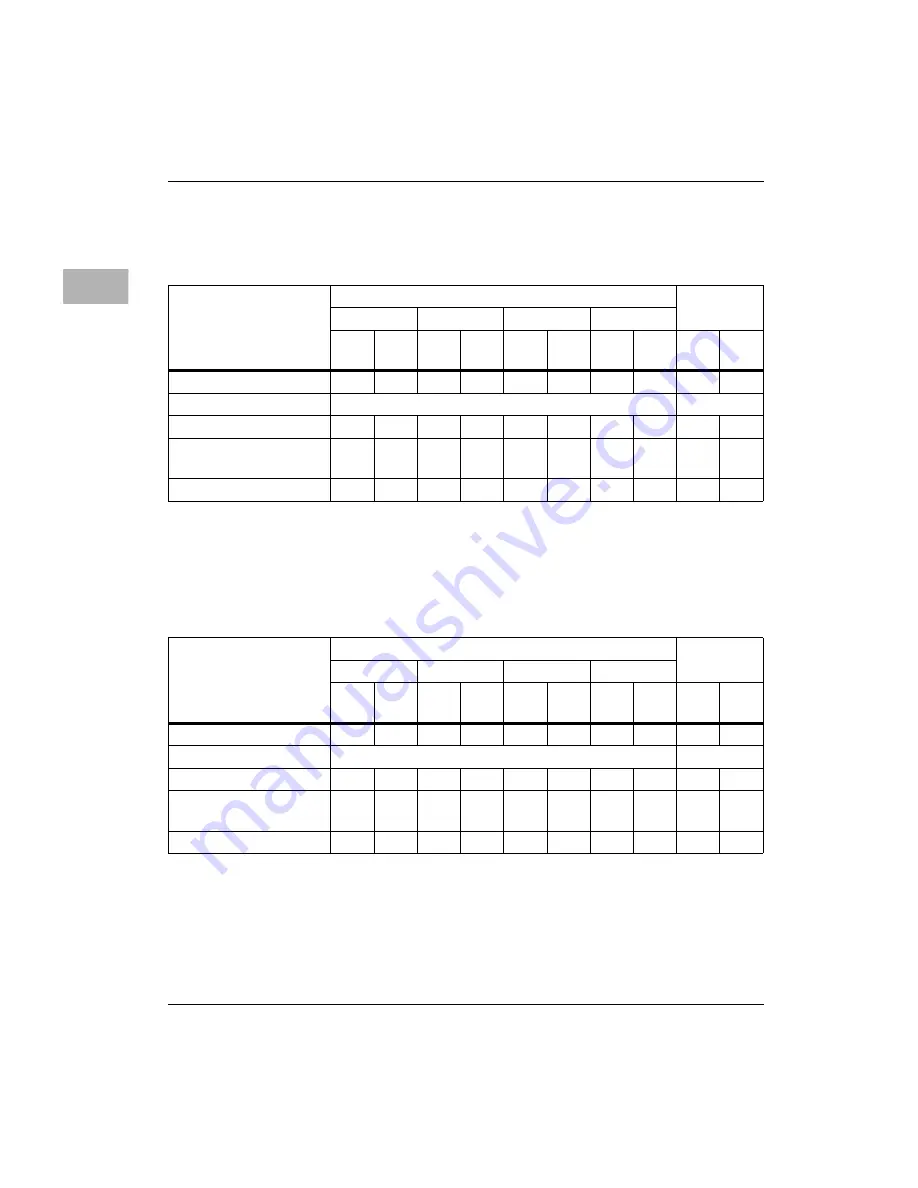

Table 3-6. PPC60x Bus to ROM/Flash Access Timing

(80ns @ 100 MHz)

ACCESS TYPE

CLOCK PERIODS REQUIRED FOR:

Total

Clocks

1st Beat

2nd Beat

3rd Beat

4th Beat

16

Bits

64

Bits

16

Bits

64

Bits

16

Bits

64

Bits

16

Bits

64

Bits

16

Bits

64

Bits

4-Beat Read

54

18

48

12

48

12

48

12

198

54

4-Beat Write

N/A

N/A

1-Beat Read (1 byte)

18

18

-

-

-

-

-

-

18

18

1-Beat Read (2 to 8

bytes)

54

18

-

-

-

-

-

-

54

18

1-Beat Write

21

21

-

-

-

-

-

-

21

21

Table 3-7. PPC60x Bus to ROM/Flash Access Timing

(50ns @ 100 MHz)

ACCESS TYPE

CLOCK PERIODS REQUIRED FOR:

Total

Clocks

1st Beat

2nd Beat

3rd Beat

4th Beat

16

Bits

64

Bits

16

Bits

64

Bits

16

Bits

64

Bits

16

Bits

64

Bits

16

Bits

64

Bits

4-Beat Read

42

15

36

9

36

9

36

9

150

42

4-Beat Write

N/A

N/A

1-Beat Read (1 byte)

15

15

-

-

-

-

-

-

15

15

1-Beat Read (2 to 8

bytes)

42

15

-

-

-

-

-

-

42

15

1-Beat Write

21

21

-

-

-

-

-

-

21

21

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...