xxvii

An asterisk (*) following a signal name for signals that are level significant

denotes that the signal is true or valid when the signal is low.

An asterisk (*) following a signal name for signals that are edge significant

denotes that the actions initiated by that signal occur on high to low

transition.

In this manual, assertion and negation are used to specify forcing a signal

to a particular state. In particular, assertion and assert refer to a signal that

is active or true; negation and negate indicate a signal that is inactive or

false. These terms are used independently of the voltage level (high or low)

that they represent.

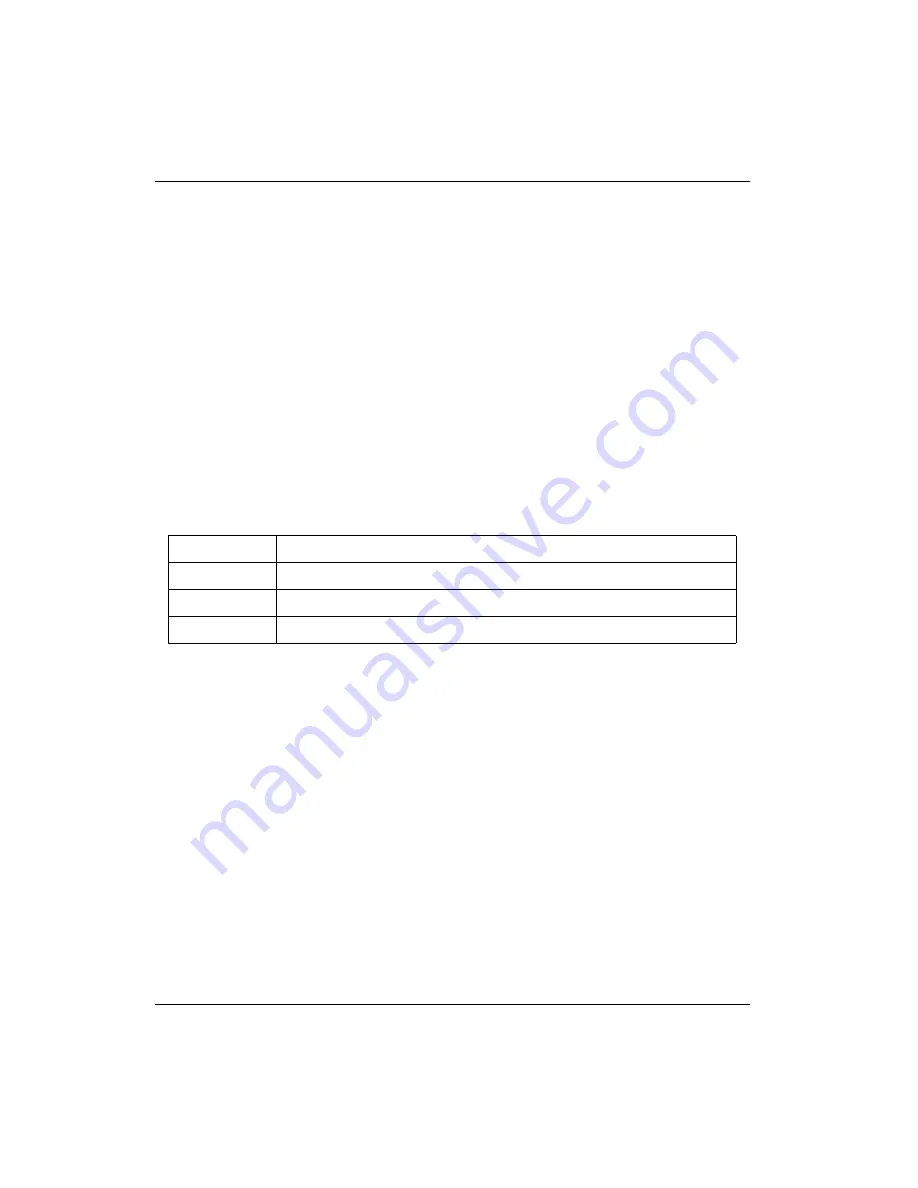

Data and address sizes are defined as follows:

%

Specifies a binary number

&

Specifies a decimal number

Byte

8 bits, numbered 0 through 7, with bit 0 being the least significant.

Half word

16 bits, numbered 0 through 15, with bit 0 being the least significant.

Word

32 bits, numbered 0 through 31, with bit 0 being the least significant.

Double word

64 bits, numbered 0 through 63, with bit 0 being the least significant.

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...