B-8

Computer Group Literature Center Web Site

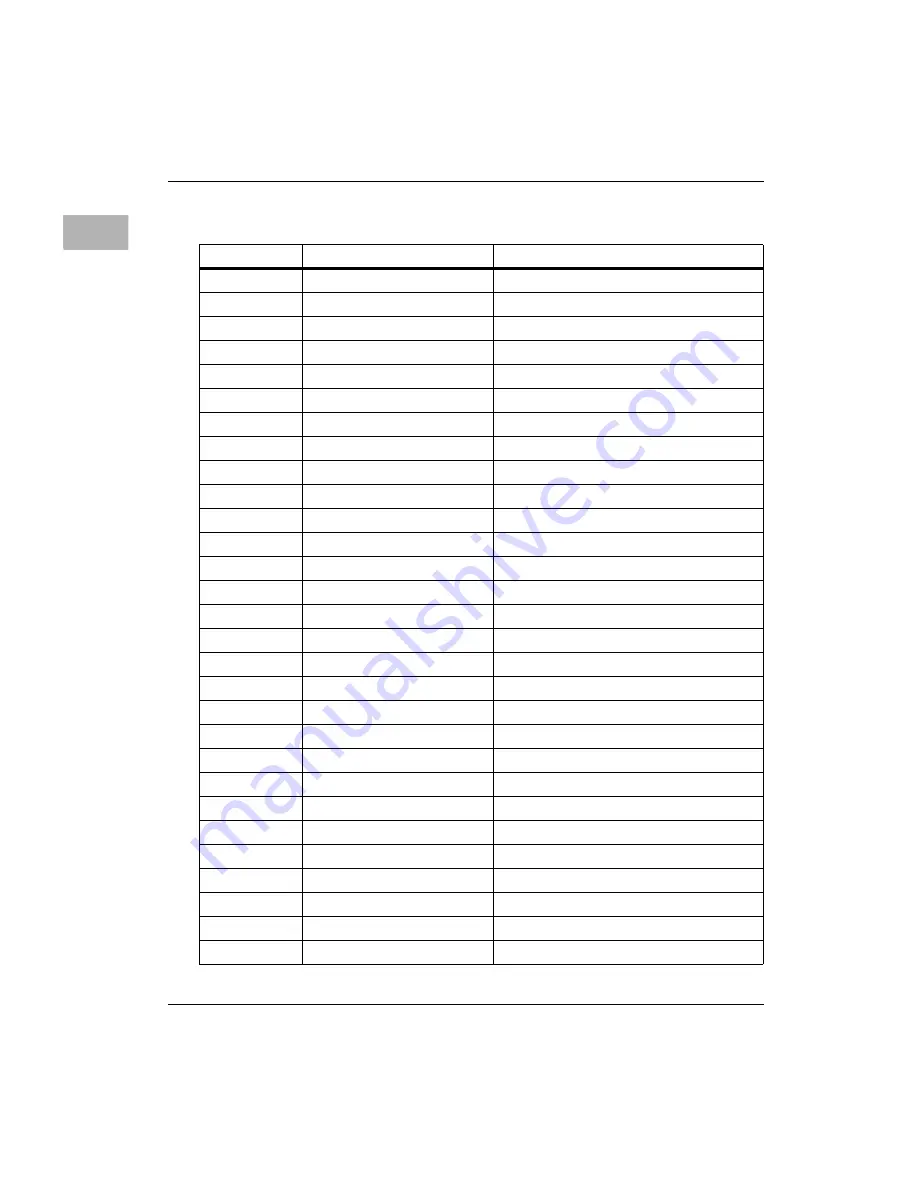

MVME5100 VPD Reference Information

B

24

PCO_SERIAL1_CONN

Serial device 1 connector present

25

PCO_SERIAL2_CONN

Serial device 2 connector present

26

PCO_SERIAL3_CONN

Serial device 3 connector present

27

PCO_SERIAL4_CONN

Serial device 4 connector present

28

PCO_FLOPPY_CONN1

Floppy device connector 1 present

29

PCO_FLOPPY_CONN2

Floppy device connector 2 present

30

PCO_PARALLEL1_CONN

Parallel device 1 connector present

31

PCO_PARALLEL2_CONN

Parallel device 2 connector present

32

PCO_PMC1_IO_CONN

PMC slot 1 I/O connector present

33

PCO_PMC2_IO_CONN

PMC slot 2 I/O connector present

34

PCO_USB0_CONN

USB channel 0 connector present

35

PCO_USB1_CONN

USB channel 1 connector present

36

PCO_KEYBOARD_CONN

Keyboard connector present

37

PCO_MOUSE_CONN

Mouse connector present

38

PCO_VGA1_CONN

VGA device 1 connector present

39

PCO_SPEAKER_CONN

Speaker connector present

40

PCO_VME_CONN

VME backplane connector present

41

PCO_CPCI_CONN

Compact PCI backplane connector present

42

PCO_ABORT_SWITCH

Abort switch present

43

PCO_BDFAIL_LIGHT

Board fail light present

44

PCO_SWREAD_HEADER

Software readable header present

45

PCO_MEMMEZ_CONN

Memory mezzanine connector present

46

PCO_PCI0_EXP_CONN

PCI bus 0 expansion connector present

47

Reserved for future configuration options

48

PCO_DIMM1_CONN

DIMM slot 1 connector present

49

PCO_DIMM2_CONN

DIMM slot 2 connector present

50

PCO_DIMM3_CONN

DIMM slot 3 connector present

51

PCO_DIMM4_CONN

DIMM slot 4 connector present

52-127

Reserved for future configuration options

Table B-2. MCG Product Configuration Options Data (Continued)

Bit Number

Bit Mnemonic

Bit Description

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...