1-4

Computer Group Literature Center Web Site

Product Data and Memory Maps

1

Memory maps

The following sections describe the memory maps for the MVME5100.

Processor Memory Map

The processor memory map configuration is under the control of the PCI

Host Bridge (PHB) and System Memory Controller (SMC) portions of the

Hawk ASIC. The Hawk adjusts system mapping to suit a given

application via programmable map decoder registers. At system power-up

or reset, a default processor memory map takes over.

Following a reset, the memory map presented to the processor is identical

to the CHRP memory map described in this document.

The MVME5100 is fully capable of supporting both the PREP and the

CHRP processor memory maps with ROM/FLASH size limited to 16MB

and RAM size limited to 2GB.

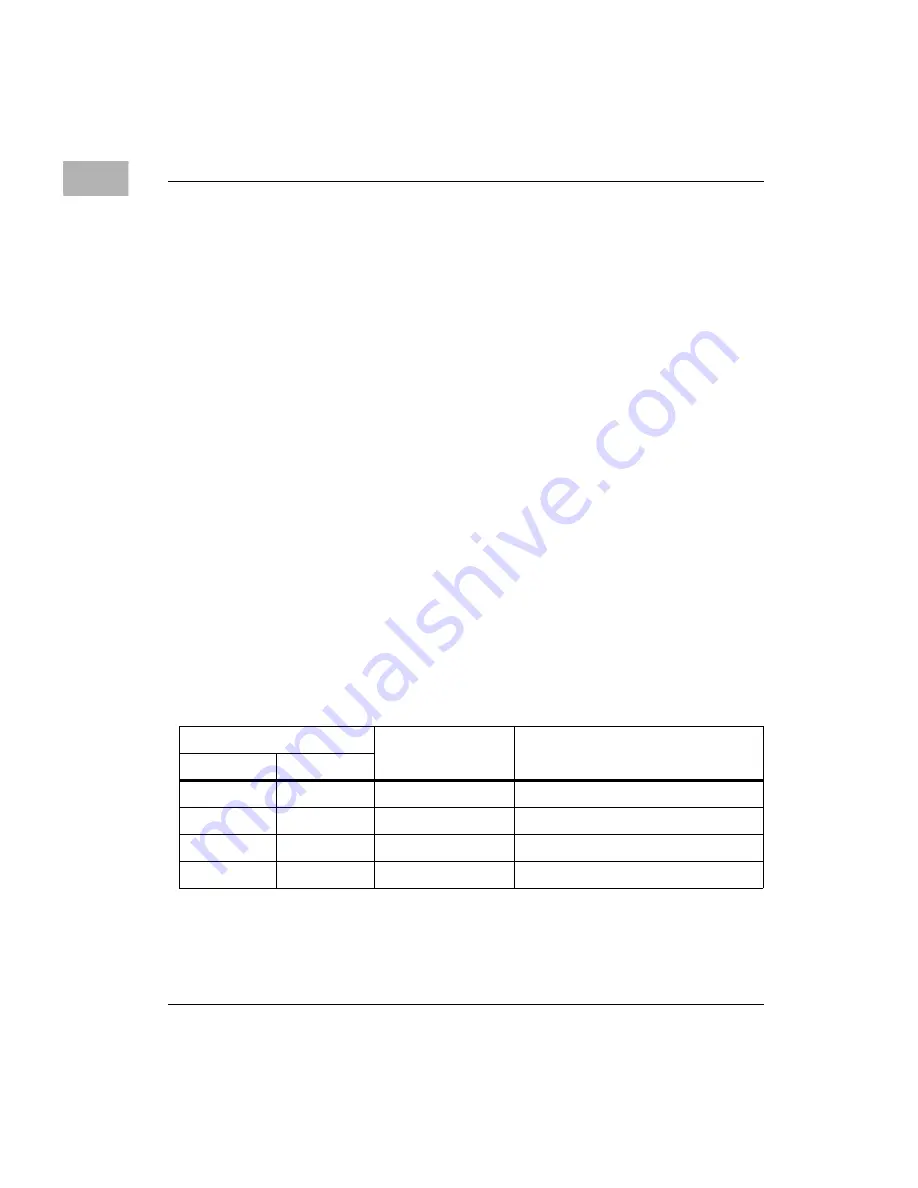

Default Processor Memory Map

The default processor memory map that is valid at power-up or reset

remains in effect until reprogrammed for specific applications.

defines the entire default map ($00000000 to $FFFFFFFF).

Table 1-2. Default Processor Memory Map

Processor Address

Size

Definition

Start

End

0000 0000

7FFF FFFF

2GB

Not Mapped

8000 0000

8080 FFFF

8M+64K

Zero-based PCI/ISA I/O Space

8081 0000

FEF7 FFFF

2GB-24MB-576KB

Not Mapped

FEF8 0000

FEF8 FFFF

64KB

System Memory Controller Registers

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...