1-6

Computer Group Literature Center Web Site

Product Data and Memory Maps

1

Notes

1. Programmable via Hawk ASIC

2. The actual PowerPlus II size of each ROM/FLASH bank may vary.

3. The first 1MB of ROM/FLASH Bank A appears at this range after

a reset if the rom_b_rv control bit is cleared. If the rom_b_rv control

bit is set this address maps to ROM/FLASH Bank B.

4. The only method to generate a PCI Interrupt Acknowledge cycle

(8259 IACK) is to perform a read access to the Hawks PIACK

Register at 0xFEFF0030.

5. VME should be placed at toe top of PCI memory space.

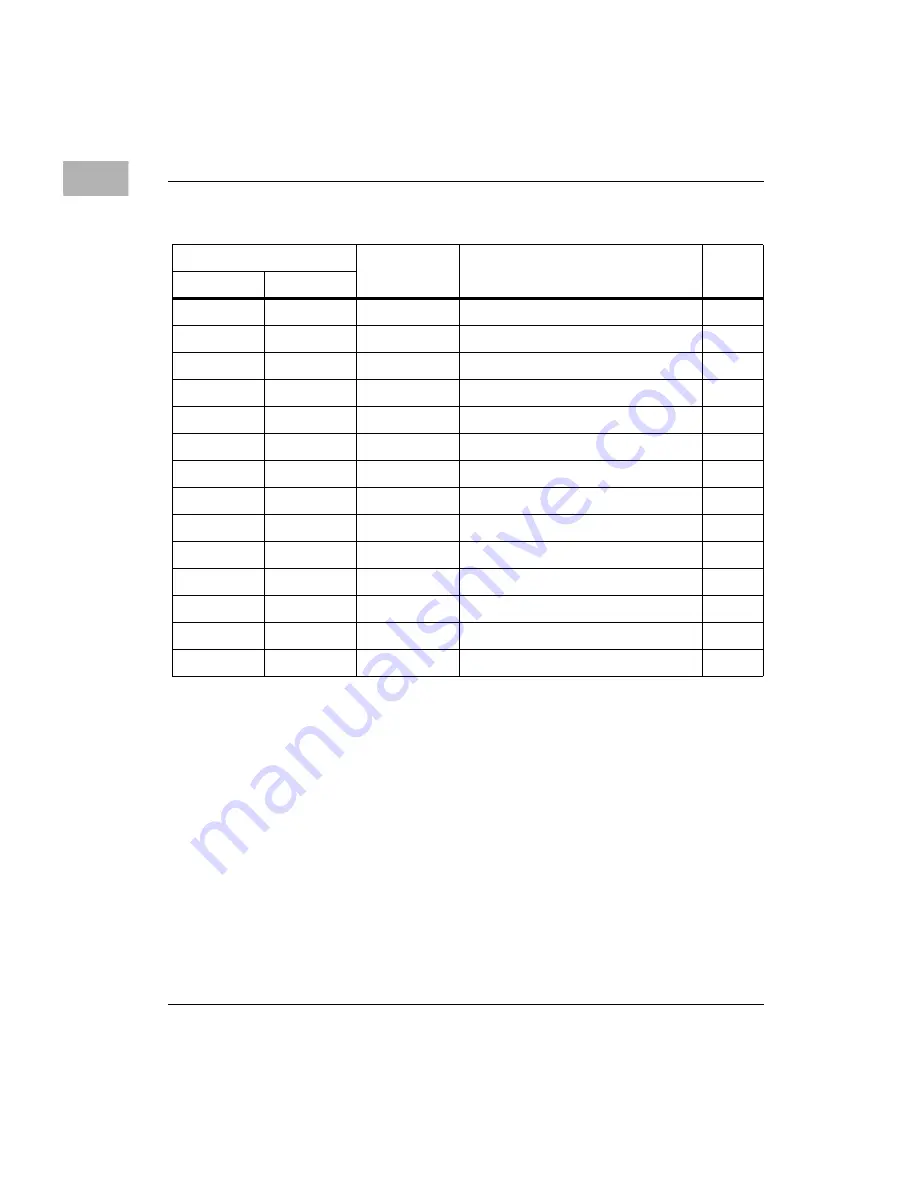

Table 1-3. Suggested CHRP Memory Map

Processor Address

Size

Definition

Notes

Start

End

0000 0000

top_dram

dram_size

System Memory (onboard DRAM)

1

top_dram

F3FF FFFF

4G-dram_size

PCI Memory Space

1, 5

F400 0000

F7FF FFFF

64MB

FLASH Bank A (optional)

1, 2

F800 0000

FBFF FFFF

64MB

FLASH Bank B (optional)

1, 2

FC00 0000

FDFF FFFF

32MB

Reserved

FE00 0000

FE7F FFFF

8MB

PCI/ISA I/O Space

1

FE80 0000

FEF7 FFFF

7.5MB

Reserved

FEF8 0000

FEF8 FFFF

64KB

System Memory Controller Registers

FEF9 0000

FEFE FFFF

384KB

Reserved

FEFF 0000

FEFF FFFF

64KB

Processor Host Bridge Registers

4

FF00 0000

FF7F FFFF

8MB

FLASH Bank A (preferred)

1, 2

FF80 0000

FF8F FFFF

1MB

FLASH Bank B (preferred)

1, 2

FF90 0000

FFEF FFFF

6MB

Reserved

FFF0 0000

FFFF FFFF

1MB

Boot ROM

3

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...