PCI Local Bus

http://www.motorola.com/computer/literature

1-27

1

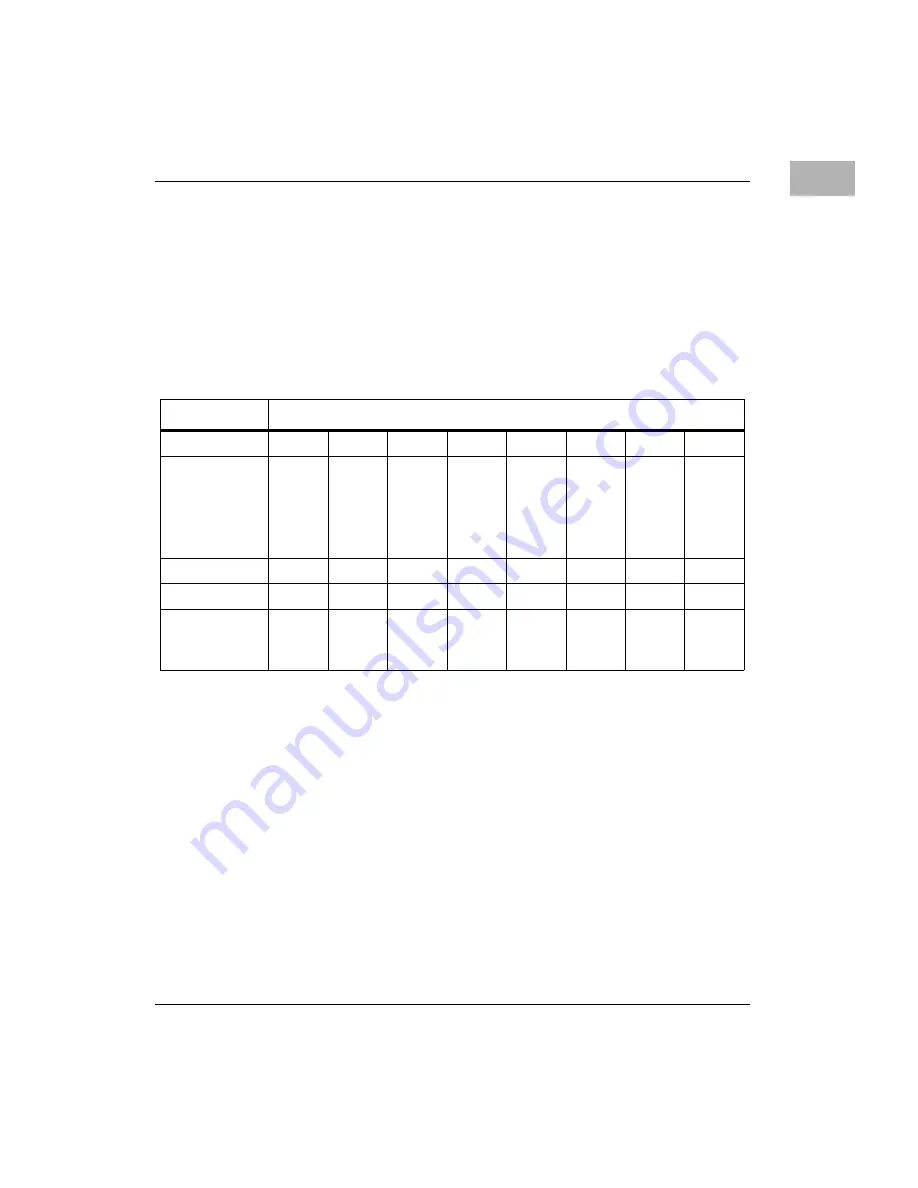

TBEN Bit Register

The MVME5100 implementation of this register is fully compliant with

the PowerPlus II Programming Specification, with exceptions to Bit RD6,

as indicated in the following table:

The TBEN Bit register provides the means to control the Processor

Timebase Enable input.

TBEN0

Processor 0 Time Base Enable. When this bit is cleared, the TBEN

pin of Processor 0 will be driven low. When this bit is set, the

TBEN pin is driven high.

TBEN1

This bit is not used.

Table 1-14. TBEN Bit Register

REG

TBEN Bit Register - Offset 80C0h

BIT

RD0

RD1

RD2

RD3

RD4

RD5

RD6

RD7

FIELD

TB

EN1

(NOT USED)

TB

EN0

OPER

R

R

R

R

R

R

R/W

R/W

RESET

X

X

X

X

X

X

1

1

REQUIRED

OR

OPTIONAL

X

X

X

X

X

X

O

R

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...