1-28

Computer Group Literature Center Web Site

Product Data and Memory Maps

1

NVRAM/RTC & Watchdog Timer

The MVME5100’s NVRAM/RTC and Watchdog Timer functions are

supplied by an M48T37V device and is fully compliant with the

PowerPlusII internal programming configuration. The M48T37V provides

32K of non-volatile SRAM, a time-of-day clock, and a watchdog timer.

Accesses to the M48T37V is accomplished via three registers: the

NVRAM/RTC Address Strobe 0 Register, the NVRAM/RTC Address

Strobe 1 Register, and the NVRAM/RTC Data Port Register. The

NVRAM/RTC Address Strobe 0 Register latches the lower 8 bits of the

address and the NVRAM/RTC Address Strobe 1 Register latches the upper

5 bits of the address

The NVRAM and RTC is accessed through the above three registers.

When accessing an NVRAM/RTC location, perform the following

procedure:

1. Write the low address (A7-A0) of the NVRAM to the

NVRAM/RTC STB0 register,

2. Write the high address (A15-A8) of the NVRAM to the

NVRAM/RTC STB1 register, and

3. Then read or write the NVRAM/RTC Data Port.

Refer to the M48T37V Data Sheet for additional details and programming

information.

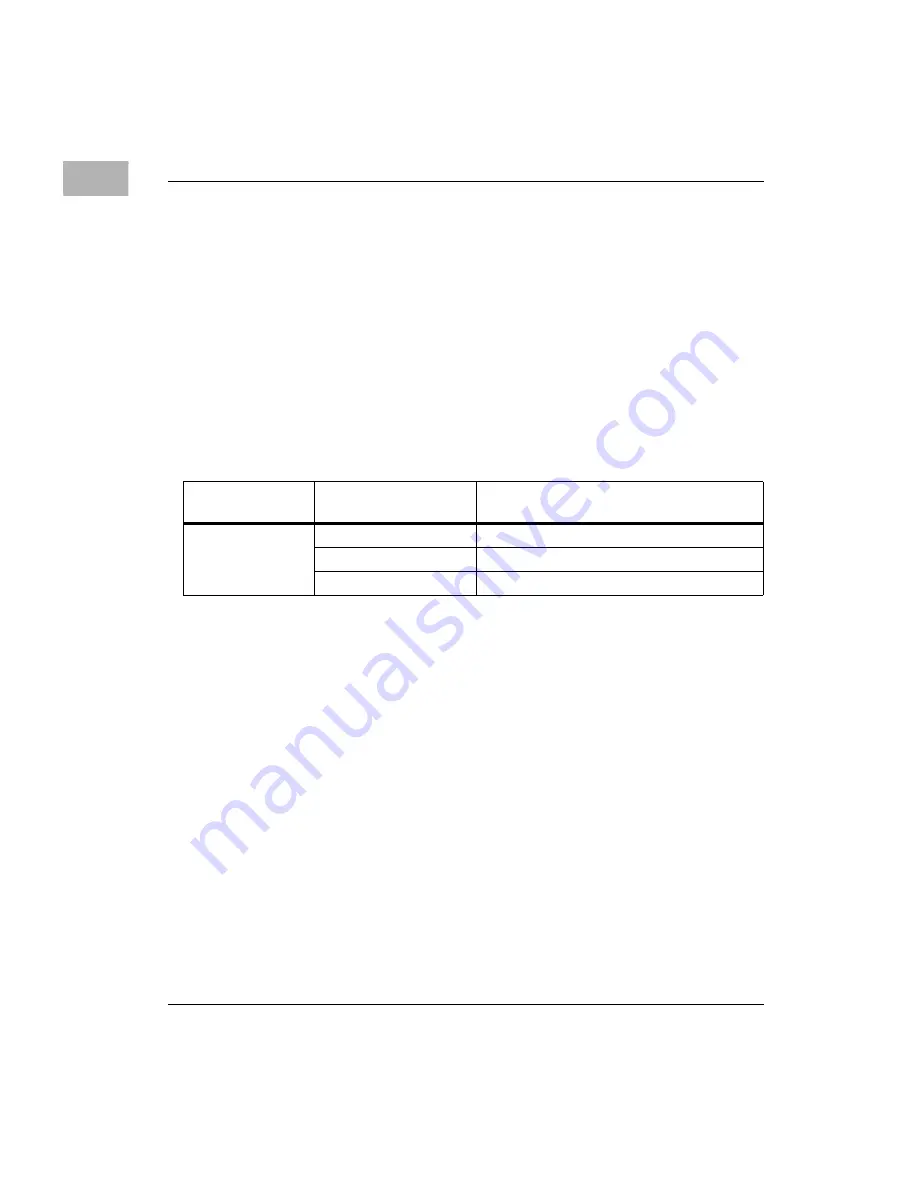

Table 1-15. M48T37V Access Registers

Required of

Optional

Offset Address

Function

This Group

Optional

80C8

NVRAM/RTC Address Strobe 0 (A7-A0)

80D0

NVRAM/RTC Address Strobe 1 (A15-A8)

80D8

NVRAM/RTC Data Register

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...