2-6

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

PPC Address Mapping

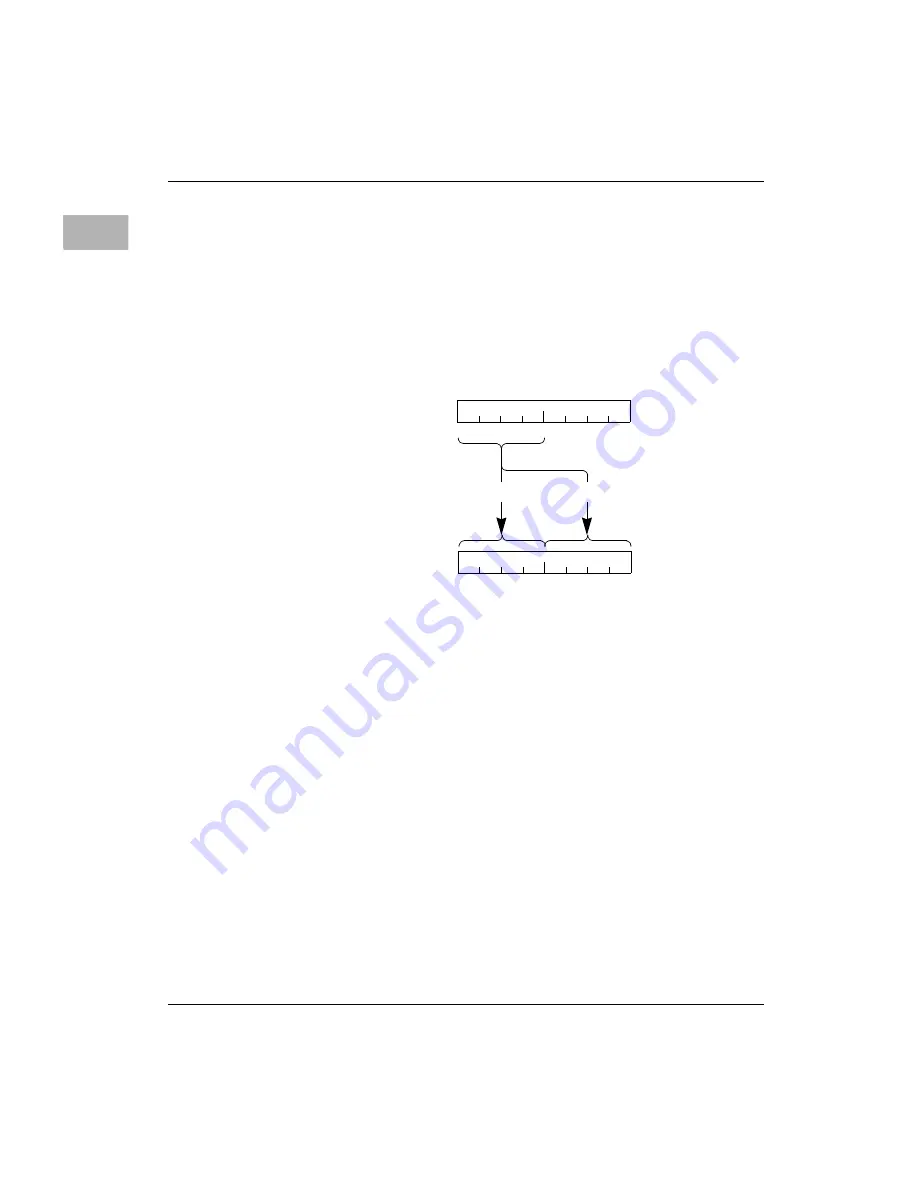

The PHB will map either PCI memory space or PCI I/O space into PPC

address space using four programmable map decoders. These decoders

provide windows of access to the PCI bus from the PPC bus. The most

significant 16 bits of the PPC address are compared with the address range

of each map decoder, and if the address falls within the specified range, the

access is passed on to the PCI. An example of this is shown in

Figure 2-2. PPC to PCI Address Decoding

There are no limits imposed by the PHB on how large of an address space

a map decoder can represent. There is a lower limit of a minimum of 64KB

due to the resolution of the address compare logic.

For each map, there is an associated set of attributes. These attributes are

used to enable read accesses, enable write accesses, enable write posting,

and define the PCI transfer characteristics.

PPC Bus Address

8 0 8 0 1 2 3 4

31

16

15

0

XSADDx Register

7 0 8 0 9 0 0 0

31

16

15

0

>=

<=

and

Decode is

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...