Functional Description

http://www.motorola.com/computer/literature

2-7

2

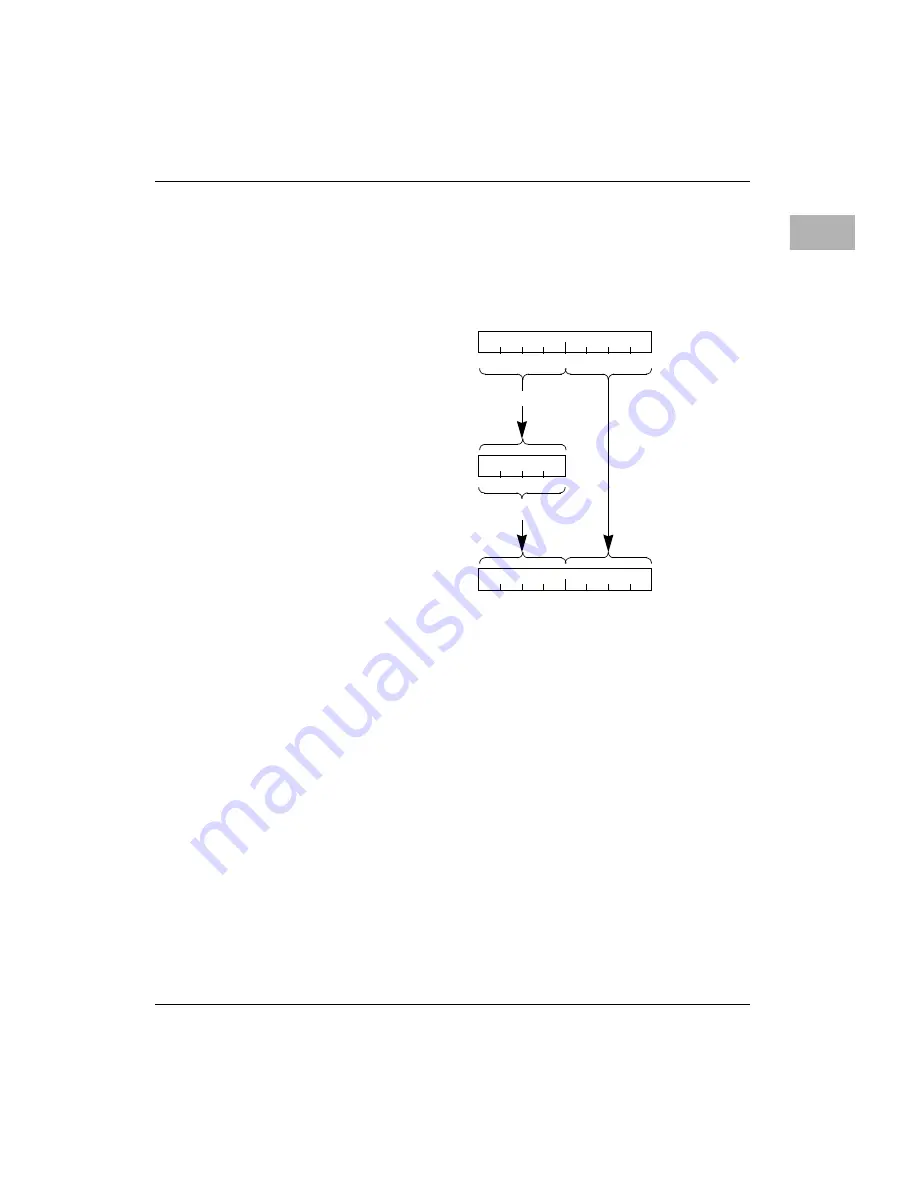

Each map decoder also includes a programmable 16-bit address offset. The

offset is added to the 16 most significant bits of the PPC address, and the

result is used as the PCI address. This offset allows PCI devices to reside

at any PCI address, independent of the PPC address map. An example of

this is shown in

Figure 2-3. PPC to PCI Address Translation

Care should be taken to ensure that all programmable decoders decode

unique address ranges since overlapping address ranges will lead to

undefined operation.

PPC Slave

The PPC slave provides the interface between the PPC bus and the PPC

FIFO. The PPC slave is responsible for tracking and maintaining

coherency in the PPC60x processor bus protocol. The actions taken by the

PPC Slave to service a transaction are dependent upon whether the

transaction is posted or compelled. During compelled transactions, such as

a read or a non-posted single beat write, the PPC Slave will hold off

asserting AACK_ and TA_ until after the transaction has completed on the

PCI bus. This has the effect of removing all levels of pipelining during

compelled PHB accesses. The interdependency between the assertion of

PPC Bus Address

8 0 8 0 1 2 3 4

31

16

15

0

XSOFFx Register

9 0 0 0

15

0

+

PCI Bus Address

1 0 8 0 1 2 3 4

0

15

16

31

=

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...