Functional Description

http://www.motorola.com/computer/literature

2-9

2

PPC FIFO

A 64-bit by 8 entry FIFO (2 cache lines total) is used to hold data between

the PPC Slave and the PCI Master to ensure that optimum data throughput

is maintained. The same FIFO is used for both read and write transactions.

A 46-bit by 4 entry FIFO is used to hold command information being

passed between the PPC Slave and the PCI Master. If write posting has

been enabled, then the maximum number of transactions that may be

posted is limited by the abilities of either the data FIFO or the command

FIFO.

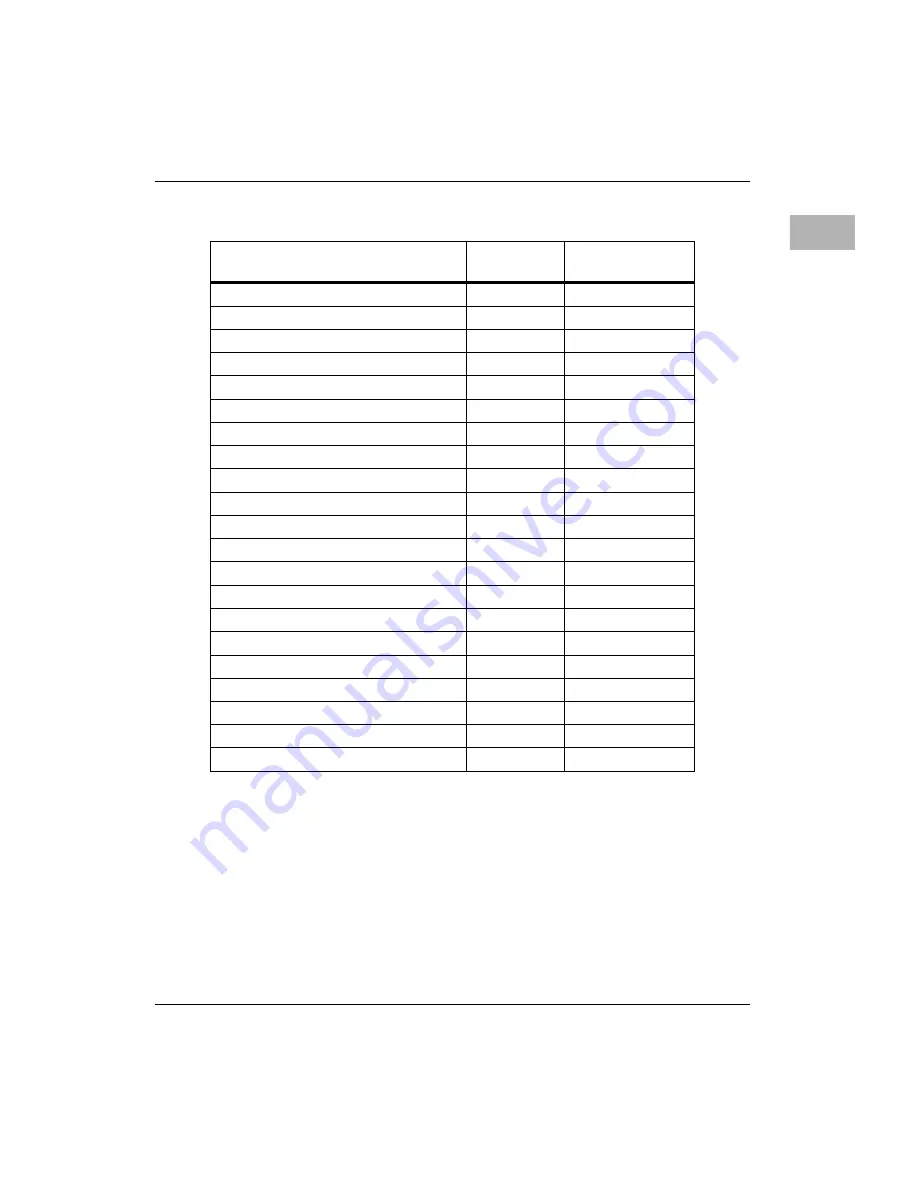

ECOWX

10100

No Response

TLB Invalidate

11000

Addr Only

ECIWX

11100

No Response

LWARX

00001

Addr Only

STWCX

00101

Addr Only

TLBSYNC

01001

Addr Only

ICBI

01101

Addr Only

Reserved

1XX01

No Response

Write-with-flush

00010

Write

Write-with-kill

00110

Write

Read

01010

Read

Read-with-intent-to-modify

01110

Read

Write-with-flush-atomic

10010

Write

Reserved

10110

No Response

Read-atomic

11010

Read

Read-with-intent-to-modify-atomic

11110

Read

Reserved

00011

No Response

Reserved

00111

No Response

Read-with-no-intent-to-cache

01011

Read

Reserved

01111

No Response

Reserved

1xx11

No Response

Table 2-1. PPC Slave Response Command Types (Continued)

PPC Transfer Type

Transfer

Encoding

Transaction

Summary of Contents for MVME5100 Series

Page 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Page 16: ...xvi ...

Page 20: ...xx ...

Page 28: ...xxviii ...

Page 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Page 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Page 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Page 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...